Digital trainer Kit Introduction link: <a href="https://www.youtube.com/watch?v=cUdKSQSxVl8">https://www.youtube.com/watch?v=cUdKSQSxVl8</a>

## **Experiment 1**

### In a battery powered computer, the diskette driver motor 1 should be ON iff

- There is a diskette in the drive

- The diskette drive door is closed

- Diskette drive motor 2 is not ON

- The battery low signal is not present and

- The computer has started a read operation, or the computer has started a write operation

Design a circuit using basic gates.

Aim: Realization of any given circuit using basic gates only.

### Components Required for the conduction of the experiment:

- Digital trainer kit.

- IC 74LS32 (2 input OR gate)

- IC 74LS08 (2 input AND gate)

- IC 74LS04 (NOT gate)

- Patch cards

#### Procedure:

- 1. Design the circuit and plot the truth table for given expression and also for solved expression and verify.

- 2. Check the all required gates whether it is working.

- 3. Label with the pin numbers for the circuit, referring IC diagram.

- 4. Connection to be done as per the circuit.

- 5. For each entry in truth table cross verify it.

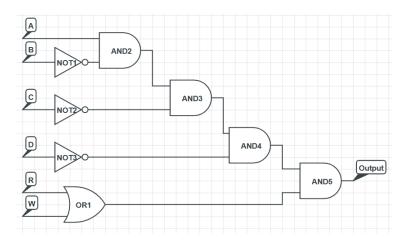

#### **Designing of circuit**

#### **Consider variables for:**

- There is a diskette in the drive: **A**

- The diskette drive door is Open: **B**

- Diskette drive motor 2 is ON: C

- The battery low signal is present: **D**

- The computer has started a read operation: **R**

- The computer has started a write operation: **W**

Output expression: A B' C' D' (R + W)

## **Truth Table:**

- Output should be high only when

| A | В | C | D | R | W | Y |

|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 |

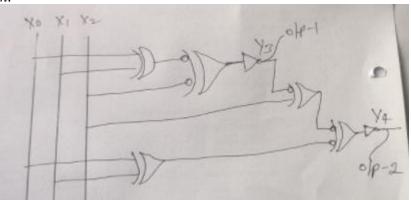

## **Circuit:**

**Result:** The given expression is verified with the help of truth table.

Experiment 1 URL: <a href="https://youtu.be/AsgpSUbaKXk">https://youtu.be/AsgpSUbaKXk</a>

You will gain weight if you eat too much or you do not exercise enough and your metabolism rate is too low. Design a system such that it alarms you when you gain weight using NAND gates.

Aim: Realization of any given circuit using NAND gates only.

### Components Required for the conduction of the experiment:

- Digital trainer kit.

- IC 7400 (2 input NAND gate)

- IC 7410 (3 input NAND gate)

- Patch cards

### Procedure:

- 1. Design the circuit and plot the truth table for given expression and also for solved expression and verify.

- 2. Check the all required gates whether it is working.

- 3. Label with the pin numbers for the circuit, referring IC diagram.

- 4. Connection to be done as per the circuit.

- 5. For each entries in truth table cross verify it.

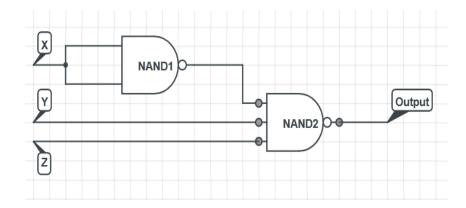

### **Designing of circuit**

#### **Consider variables for:**

Eat: XExercise: YMetabolism: Z

### **Truth Table:**

| X | Y | Z | OUTPUT |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 1      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 0      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 1      |

# Karnaugh Map simplification

| X\YZ | Y'Z' | Y'Z | YZ | YZ' |  |

|------|------|-----|----|-----|--|

| X'   | 1    | 1   | 0  | 1   |  |

| X    | 1    | 1   | 1  | 1   |  |

Output Expression: X + Y' + Z'

Using only NAND gates: ((X + Y' + Z')')'= (X'.Y.Z)'

### **Circuit:**

### Result:

The given expression is verified with the help of truth table.

Experiment 2 URL: https://youtu.be/b38JMmdFMcI

# The circuit breaker will trip iff

- The hair drier is turned ON

- The microwave oven is used

- All the lights in the room are ON or

- There is a short circuit in any appliance

Solve the above issue using relevant MUX.

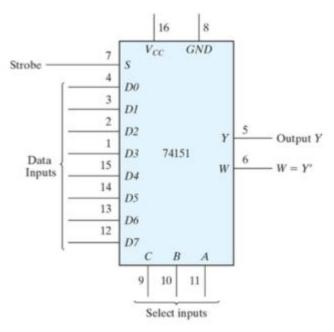

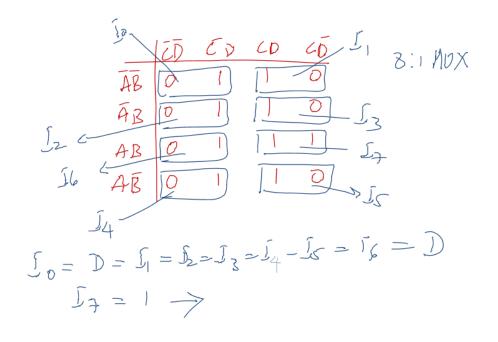

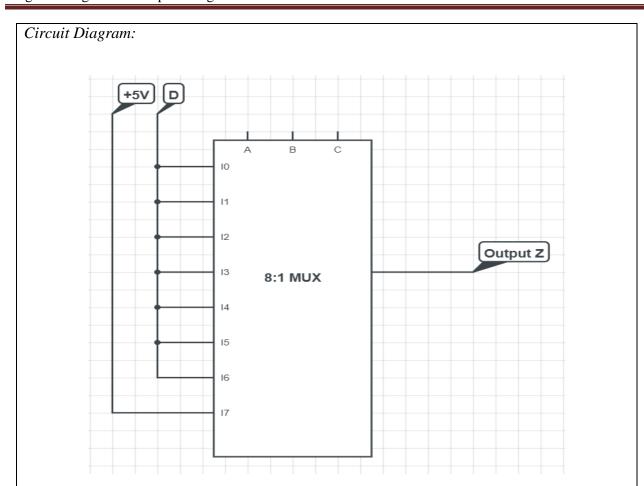

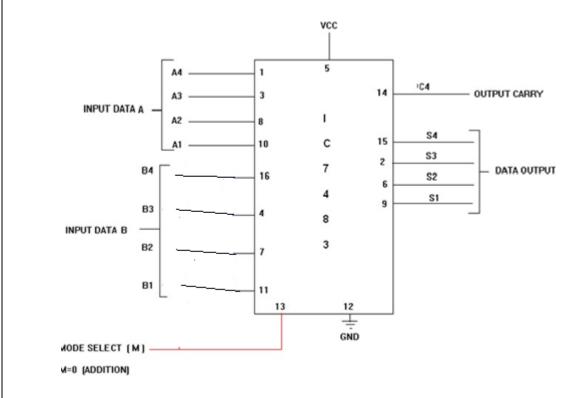

Aim: Realization of a given circuit using a 8:1 Multiplexer.

### Components Required for the conduction of the experiment:

- Digital trainer kit.

- IC 74LS151 (8:1 Multiplexer)

- Patch cards

## Pin Diagram: 74151

#### **Procedure:**

- 1. Design the circuit and plot the truth table for given expression and also for solved expression and verify.

- 2. Check the all required gates whether it is working.

- 3. Label with the pin numbers for the circuit, referring IC diagram.

- 4. Connection to be done as per the circuit.

- 5. For each entries in truth table cross verify it.

|       | . 1 |   | 7 7 | 7  |

|-------|-----|---|-----|----|

| Tru   | th  | • | nh  | 10 |

| 1 I U | uii |   | uv  | ıc |

| A | В | С | D | Output |

|---|---|---|---|--------|

| 0 | 0 | 0 | 0 | 0      |

| 0 | 0 | 0 | 1 | 1      |

| 0 | 0 | 1 | 0 | 0      |

| 0 | 0 | 1 | 1 | 1      |

| 0 | 1 | 0 | 0 | 0      |

| 0 | 1 | 0 | 1 | 1      |

| 0 | 1 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1 | 1      |

| 1 | 0 | 0 | 0 | 0      |

| 1 | 0 | 0 | 1 | 1      |

| 1 | 0 | 1 | 0 | 0      |

| 1 | 0 | 1 | 1 | 1      |

| 1 | 1 | 0 | 0 | 0      |

| 1 | 1 | 0 | 1 | 1      |

| 1 | 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 1 | 1      |

# K – map Simplification

# Result:

The given expression is verified with the help of truth table.

Experiment 3 URL: <a href="https://youtu.be/ytqBeBsHuzI">https://youtu.be/ytqBeBsHuzI</a>

In an automated house, two lamps L1 and L2 are controlled by 3 switches: A, B, C. Any one of the lamps should be ON, following the below conditions

- L1 is ON if switch A and B are open but not C

- L1 is ON if switch B and C are open but not A

- L2 is ON if only switch C is open

- L2 is ON if only switch B is open

- L2 is ON if switch A or C is open, but not B

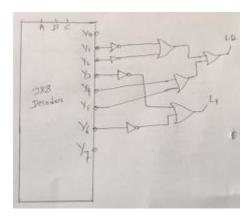

Design a circuit to make the lamp ON using decoder

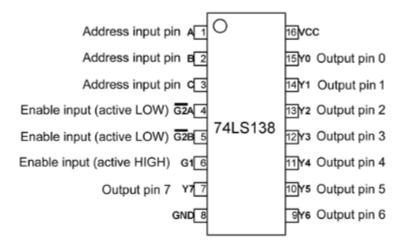

Aim: Realization of a given circuit using a decoder.

### Components Required for the conduction of the experiment:

- Digital trainer kit.

- IC 74LS138 (3:8 Decoder)

- IC 74LS32 (2 input OR gate)

- IC 74LS04(NOT gate)

- Patch cards

### Pin Diagram 74LS138

#### **Procedure:**

- 1. Design the circuit and plot the truth table for given expression and also for solved expression and verify.

- 2. Check the all required gates whether it is working.

- 3. Label with the pin numbers for the circuit, referring IC diagram.

- 4. Connection to be done as per the circuit.

- 5. For each entries in truth table cross verify it.

# Truth Table:

| A | В | C | L1 | L2 |

|---|---|---|----|----|

| 0 | 0 | 0 | 0  | 0  |

| 0 | 0 | 1 | 0  | 1  |

| 0 | 1 | 0 | 0  | 1  |

| 0 | 1 | 1 | 1  | 0  |

| 1 | 0 | 0 | 0  | 1  |

| 1 | 0 | 1 | 0  | 1  |

| 1 | 1 | 0 | 1  | 0  |

| 1 | 1 | 1 | 0  | 0  |

# Circuit Diagram:

# Result:

The given expression is verified with the help of truth table.

Experiment 4 URL: <a href="https://youtu.be/FhLRjJ0YbNY">https://youtu.be/FhLRjJ0YbNY</a>

Assume you are generating and transmitting binary data from one place to another. Check whether the sent data is transmitted properly.

Aim: Realization of parity generator and checker.

### Components Required for the conduction of the experiment:

- Digital trainer kit.

- IC 74LS86 (XOR)

- IC 74LS04 (NOT)

- Patch cards

#### Procedure:

- 1. Design the circuit and plot the truth table for given expression and for solved expression and verify.

- 2. Check the all required gates whether it is working.

- 3. Label with the pin numbers for the circuit, referring IC diagram.

- 4. Connection to be done as per the circuit.

- 5. For each entries in truth table cross verify it.

## Truth table for ODD parity generator

| X2 | X1 | X0 | <i>Y3</i> | Y2 | <i>Y1</i> | <i>Y0</i> |

|----|----|----|-----------|----|-----------|-----------|

| 0  | 0  | 0  | 1         | 0  | 0         | 0         |

| 0  | 0  | 1  | 0         | 0  | 0         | 1         |

| 0  | 1  | 0  | 0         | 0  | 1         | 0         |

| 0  | 1  | 1  | 1         | 0  | 1         | 1         |

| 1  | 0  | 0  | 0         | 1  | 0         | 0         |

| 1  | 0  | 1  | 1         | 1  | 0         | 1         |

| 1  | 1  | 0  | 1         | 1  | 1         | 0         |

| 1  | 1  | 1  | 0         | 1  | 1         | 1         |

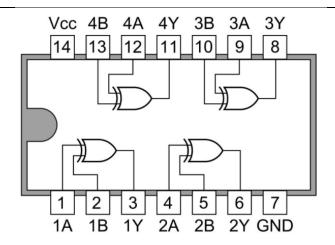

Pin Diagram of 7486

Circuit Diagram:

Odd Parity Checker

# Result:

The given expression is verified with the help of truth table.

Experiment URL: <a href="https://youtu.be/t-q3BRSNG\_A">https://youtu.be/t-q3BRSNG\_A</a>

Assume you need to send a secret message consisting of numbers from 1 to 9 and letters from A to F. Secret message is encoded using excess 3 code. Design a circuit using ADDER IC to send a secret message to your friend.

Aim: Realization of Excess 3 to BCD and vice-versa using adder.

# Components Required for the conduction of the experiment:

- Digital trainer kit.

- IC 74LS83(4 bit Adder IC)

- IC 74LS86 (XOR)

- Patch cards

#### **Procedure:**

#### Case 1: BCD to Excess-3 code converter

- Check all the pins by connecting them and testing it with their respective truth tables.

- Label the pin diagram by referring the circuit diagram for the IC pins.

- Connect the IC's according to the pin diagram.

- Make Cin as 0 and bit B=3 i.e.B3, B2, B1, B0 = 0.0.1.1.

- For each entry in the truth table, verify the values corresponding to it.

#### Case 2: Excess-3 to BCD code converter

- Check all the pins by connecting them and testing it with their respective truth tables.

- Label the pin diagram by referring the circuit diagram for the IC pins.

- Connect the IC's according to the pin diagram.

- Make Cin as 1 and bit B=3 i.e. B3, B2, B1, B0 = 0011.

- For each entry in the truth table, verify the values corresponding to it.

#### **Truth Table**

### BCD to Excess – 3:

Cin = 0, B = 3 i.e.  $B_3 B_2 B_1 B_0 = 1 1 0 1 (2's complement of 0 0 1 1)$

|           | INP       | UT |           | OUTPUT    |           |    |    |  |

|-----------|-----------|----|-----------|-----------|-----------|----|----|--|

| <b>A3</b> | <b>A2</b> | A1 | <b>A0</b> | <b>S3</b> | <b>S2</b> | S1 | S0 |  |

| 0         | 0         | 0  | 0         | 0         | 0         | 1  | 1  |  |

| 0         | 0         | 0  | 1         | 0         | 1         | 0  | 0  |  |

| 0         | 0         | 1  | 0         | 0         | 1         | 0  | 1  |  |

| 0         | 0         | 1  | 1         | 0         | 1         | 1  | 0  |  |

| 0         | 1         | 0  | 0         | 0         | 1         | 1  | 1  |  |

| 0         | 1         | 0  | 1         | 1         | 0         | 0  | 0  |  |

| 0         | 1         | 1  | 0         | 1         | 0         | 0  | 1  |  |

| 0         | 1         | 1  | 1         | 1         | 0         | 1  | 0  |  |

| 1         | 0         | 0  | 0         | 1         | 0         | 1  | 1  |  |

| 1         | 0         | 0  | 1         | 1         | 1         | 0  | 0  |  |

Excess – 3 to BCD:

$C_{in} = 1$ , B = 3 i.e.  $B_3 B_2 B_1 B_0 = 0 0 1 1$

|           | INP       | PUT       |           | OUTPUT    |           |    |    |  |

|-----------|-----------|-----------|-----------|-----------|-----------|----|----|--|

| <b>A3</b> | <b>A2</b> | <b>A1</b> | <b>A0</b> | <b>S3</b> | <b>S2</b> | S1 | S0 |  |

| 0         | 0         | 1         | 1         | 0         | 0         | 0  | 0  |  |

| 0         | 1         | 0         | 0         | 0         | 0         | 0  | 1  |  |

| 0         | 1         | 0         | 1         | 0         | 0         | 1  | 0  |  |

| 0         | 1         | 1         | 0         | 0         | 0         | 1  | 1  |  |

| 0         | 1         | 1         | 1         | 0         | 1         | 0  | 0  |  |

| 1         | 0         | 0         | 0         | 0         | 1         | 0  | 1  |  |

| 1         | 0         | 0         | 1         | 0         | 1         | 1  | 0  |  |

| 1         | 0         | 1         | 0         | 0         | 1         | 1  | 1  |  |

| 1         | 0         | 1         | 1         | 1         | 0         | 0  | 0  |  |

| 1         | 1         | 0         | 0         | 1         | 0         | 0  | 1  |  |

# Circuit Diagram:

### Result:

The truth table is verified.

https://youtu.be/CdJ0mJkbKRU

Consider a computer operator who needs to generate a sequence 1011 continuously which is transmitted across the network. Design a circuit to implement this job.

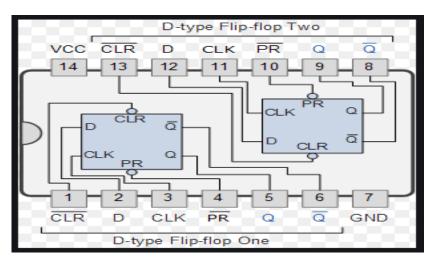

Aim: Realization of a shift register.

### Components Required for the conduction of the experiment:

- Digital trainer kit.

- IC 7474 (D Flip Flops)

- Patch cards

## Pin Diagram of D Flip-Flop

#### Procedure:

- 1. Design the circuit and plot the truth table for given expression and also for solved expression and verify.

- 2. Check the all required gates whether it is working.

- 3. Label with the pin numbers for the circuit, referring IC diagram.

- 4. Connection to be done as per the circuit.

- 5. For each entry in truth table cross verify it.

# Truth Table:

| Clock | Serial<br>input | $\mathbf{Q}_0$ | $Q_1$      | $\mathbf{Q}_2$ | $\mathbf{Q}_3$ |

|-------|-----------------|----------------|------------|----------------|----------------|

| 0     | 1               | 0              | 0          | 0              | 0              |

| 1     | 0               | <b>^</b> 1 ,   | <b>^</b> 0 | <b>,</b> 0/    | 0              |

| 2     | 1               | • 0            | 1          | 0              | <b>^</b> 0     |

| 3     | 1               | 1              | 0          | 1              | •0             |

| 4     |                 | <b>1</b>       | 1          | 0              | 1              |

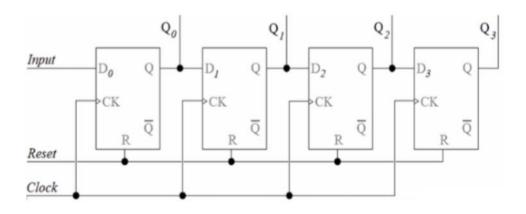

# Circuit Diagram:

## Result:

The given expression is verified with the help of truth table.

URL: https://youtu.be/ouv4Y6ZwKR8

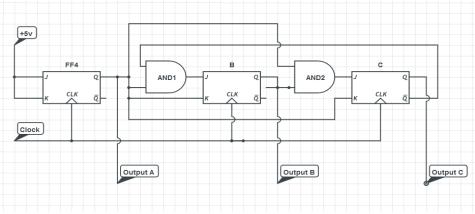

Consider a scenario where in you want to take print out of few selected random pages in sequence numbered from 0 to 5. Design a circuit to achieve this task using J-K Flipflops.

Aim: Realization of a counting sequence using JK flipflops

### Components Required for the conduction of the experiment:

- Digital trainer kit.

- IC 74LS76 (JK Flipflop)

- IC 74LS08 (AND Gate)

- Patch cards

#### **Procedure:**

- 1. Design the circuit and plot the truth table for given expression and also for solved expression and verify.

- 2. Check the all required gates whether it is working.

- 3. Label with the pin numbers for the circuit, referring IC diagram.

- 4. Connection to be done as per the circuit.

- 5. For each entry in truth table cross verify it.

### **Designing of circuit**

### J - K flip – flop excitation table:

| Present state | Next<br>state | J | K |

|---------------|---------------|---|---|

| 0             | 0             | 0 | X |

| 0             | 1             | 1 | X |

| 1             | 0             | X | 1 |

| 1             | 1             | X | 0 |

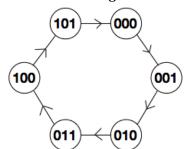

### State Transition Diagram:

| Cn | B <sub>n</sub> | A <sub>n</sub> | $C_{n+1}$ | $B_{n+1}$ | $A_{n+1}$ | $\mathbf{J}_{\mathbf{C}}$ | K <sub>C</sub> | $J_{B}$ | K <sub>B</sub> | $J_A$ | KA |

|----|----------------|----------------|-----------|-----------|-----------|---------------------------|----------------|---------|----------------|-------|----|

| 0  | 0              | 0              | 0         | 0         | 1         | 0                         | X              | 0       | X              | 1     | X  |

| 0  | 0              | 1              | 0         | 1         | 0         | 0                         | X              | 1       | X              | X     | 1  |

| 0  | 1              | 0              | 0         | 1         | 1         | 0                         | X              | X       | 0              | 1     | X  |

| 0  | 1              | 1              | 1         | 0         | 0         | 1                         | X              | X       | 1              | X     | 1  |

| 1  | 0              | 0              | 1         | 0         | 1         | X                         | 0              | 0       | X              | 1     | X  |

| 1  | 0              | 1              | 0         | 0         | 0         | X                         | 1              | 0       | X              | X     | 1  |

| BA<br>C | B'A' | B'A | ВА | BA' |

|---------|------|-----|----|-----|

| C'      | 0    | 0   | 1  | 0   |

| С       | Х    | Х   | Х  | Х   |

| BA<br>C | B'A' | B'A | ВА | BA' |

|---------|------|-----|----|-----|

| C'      | Х    | Х   | Х  | Х   |

| С       | 0    | 1   | Х  | Х   |

$J_C=BA$

| $K_B=A$ |

|---------|

|---------|

| C BA | B'A' | B'A | ВА | BA' |

|------|------|-----|----|-----|

| C'   | 0    | 1   | X  | Х   |

| С    | 0    | 0   | X  | Х   |

| BA C | B'A' | B'A | ВА | BA' |

|------|------|-----|----|-----|

| C'   | X    | X   | 1  | 0   |

| С    | Х    | Х   | Х  | Х   |

$J_B=C'A$

| <b>T</b> Z   | - A     |

|--------------|---------|

| <b>IX</b> B= | $\Xi A$ |

| BA<br>C | B'A' | B'A | ВА | BA' |

|---------|------|-----|----|-----|

| C'      | 1    | Х   | Х  | 1   |

| С       | 1    | Х   | Х  | X   |

| BA<br>C | B'A' | B'A | ВА | BA' |

|---------|------|-----|----|-----|

| C'      | X    | 1   | 1  | X   |

| С       | Х    | 1   | Х  | х   |

$J_A=1$

$K_A=1$

# Circuit:

Result:

The given expression is verified with the help of truth table.

https://youtu.be/bLhKrLdpkBY