# **Field Effect Transistors**

#### 3.1 Introduction:

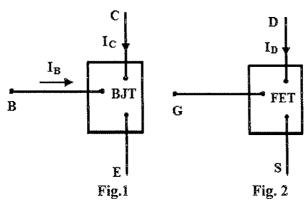

- The Field Effect Transistor abbreviated as FET is an another semiconductor device like a BJT which can be used as an amplifier or switch. Like BJT, FET is also a three terminal device. However, the principle of operation FET is completely different from that of BJT.

- The three terminals of FET's are named as: **Drain (D)**, **Source (S) and Gate (G)**, as shown in Fig. 2. Out of these terminals gate terminal acts as a controlling terminal.

- In BJT the output current,  $I_C$  is controlled by the base current  $I_B$ . Hence BJT is a current controlled device. On the other hand, in FET, the voltage applied between gate and source ( $V_{GS}$ ) controls the output current  $I_D$  therefore; FET is a voltage controlled device.

- The name "Field Effect" is derived from the fact that the output current flow is controlled by an electric field set up in the device by an externally applied voltage between gate and source terminals (V<sub>GS</sub>).

- BJT is called a bipolar device because here, the conduction of current is due to both electrons and holes (both Majority & Minority charge carriers). However, FET is called a **unipolar device** because here, the conduction of current is only due to majority charge carriers. (electrons in n-JFET and holes in p JFET).

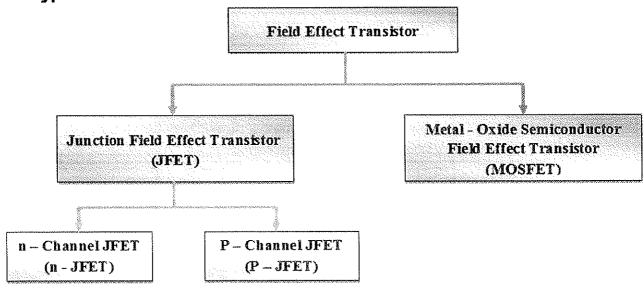

## 3.2 Types of FET:

## 3.3 Schematic symbol of JFET:

Figure 3 & 4 shows the schematic symbol of JFET. In an n-channel JFET, the arrow points towards the vertical line (shown in Fig. 3) and in p-channel JFET, the arrow points away from the vertical line (shown in Fig. 4). The vertical line represents the channel.

Fig. 3 n-channel JFET

Fig. 4 p-channel JFET

## 3.4 Comparison of BJT & FET:

|     | ВЈТ                                                                                                    |     | FET                                                                                                                                  |                  |

|-----|--------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1)  | BJT is a current controlled device.                                                                    |     | JFET is a voltage controlled device.                                                                                                 |                  |

| 2)  | Two types of transistors are npn & pnp type.                                                           |     | Two types of transistors are n-JFET & p-JFET.                                                                                        |                  |

| 3)  |                                                                                                        |     |                                                                                                                                      |                  |

|     |                                                                                                        | BE  | G N Channel JFET                                                                                                                     | G P Channel SPET |

|     | npn                                                                                                    | pnp |                                                                                                                                      |                  |

| 4)  | BJT is a Bipolar device.                                                                               |     | FET is an Unipolar device.                                                                                                           |                  |

| 5)  | Input impedance is low.                                                                                |     | Input impedance is high.                                                                                                             |                  |

| 6)  | BJTs are less temperature stable.  Bigger in size.  More sensitivity to changes in the applied signal. |     | FETs are more temperature stable.  Smaller in size, hence suitable for IC chips.  Less sensitivity to changes in the applied signal. |                  |

| 7)  |                                                                                                        |     |                                                                                                                                      |                  |

| 8)  |                                                                                                        |     |                                                                                                                                      |                  |

| 9)  | Thermal runaway may occur.                                                                             |     | Thermal runaway does not occur.                                                                                                      |                  |

| 10) |                                                                                                        |     | Input and output relation is non linear.                                                                                             |                  |

| JEET                                                | ВЈТ                                                          |

|-----------------------------------------------------|--------------------------------------------------------------|

| source $S$ drain $D$ gate $G$ drain supply $V_{DD}$ | emitter $E$ collector $C$ base $B$ collector supply $V_{CC}$ |

| gate supply $V_{GG}$ drain current $i_D$            | base supply $V_{BB}$ collector current $i_C$                 |

# 3.5 Reasons for popularity:

- Operation of FET is very simple (as compared to BJT).

- Design or fabrication is much simpler. It can be fabricated in fewer steps.

- Occupy small space (the area required for a single FET on chip is 1/5<sup>th</sup> of BJT).

- It consumes low power (in micro watts).

**NOTE**: The thickness of the depletion region increases as the reverse bias voltage across the junction is increased. The extension of the depletion region depends on the doping levels of p-type & n-type semiconductors. If both the regions are equally doped, the depletion region will extend equally on both the regions. However, if one of the regions is heavily doped in comparison with the other region, the depletion region extends more into the region of lower doping.

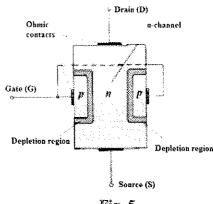

## 3.6 Construction and characteristics of n-channel JFET:

- The basic construction of the n-channel JFET is shown in Fig. 5. The major part of the structure is the *n*-type material that forms the channel between the embedded layers of *p*-type material. (here *p*-type materials are heavily doped)

- The top of the *n*-type channel is connected through an ohmic contact to a terminal referred to as the **drain** (**D**), while the lower end of the same material is connected through an ohmic contact to a terminal referred to as the **source** (**S**), both the p-type regions are connected internally and a single wire is taken out in the form of a terminal called the **gate** (**G**).

Fig. 5

• In the absence of any applied potentials (under no-bias conditions) the JFET has two *p-n* junctions. The result is a depletion region at each junction as shown in Fig. 5. Depletion does not allow majority carriers to flow through the region, but field created can control the majority carriers through the channel.

The following FET notation is worth remembering:

- <u>Source</u>: The Source S is the terminal through which majority carriers enter the channel (n region). Conventional current leaving the channel is designated by Is. Since majority carriers come from it, it is called source.

- <u>Drain</u>: The drain D is the terminal through which the majority carriers leave the region that is they are drained out from this terminal. Conventional current entering the region at D is designated by ID. The drain to source voltage is called VDS.

- Gate: On both the sides of the n-type region of Fig.5, heavily doped regions of p (that is p<sup>+</sup>) are grown that creates p-n junctions. These two p-type materials are connected together (internally shorted) and a single wire is taken out in the form of a terminal called a gate. Between the gate & source a voltage V<sub>GS</sub> is applied. (Here, both the gate terminals are connected together that means when we apply a voltage, the voltage will apply simultaneously on both the gates)

- <u>Channel</u>: It is the space or region between the two gate regions (two p regions) through which majority carriers move from source to drain when V<sub>DS</sub> is applied.

**NOTE:** The construction of p-channel JFET is similar to that of n-channel JFET, consisting of p type channel and n type gate.

## 3.6.1 Operation (Working) of n-channel JFET:

Let us now consider an n-channel JFET and discuss its working:

#### (1) When $V_{GS} = 0$ and $V_{DS} = 0$

In this case, drain current  $I_D = 0$ , because  $V_{DS} = 0$ . The depletion regions around the p-n junctions are of equal thickness and symmetrical as shown in Fig. 5.

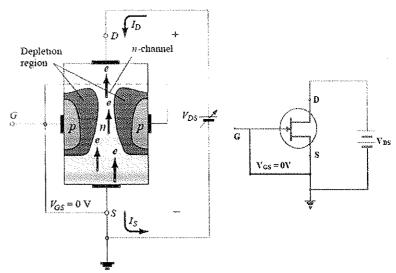

#### (2) When $V_{GS} = 0$ and $V_{DS}$ is increased from zero ( $V_{DS}$ some positive value)

- In Fig. 6, a positive voltage  $V_{DS}$  has been applied across the channel and the gate has been connected directly to the source to establish the condition  $V_{GS}=0$  V.

- The result is a gate and source terminal at the same potential and a depletion region in the low end of each p-material (near to the source region) similar to the distribution of the no-bias conditions of Fig. 5.

- The voltage V<sub>DS</sub> is applied across drain to source. The drain is made positive with respect to source.

- The instant the voltage  $V_{DS}$  is applied, The electrons (which are the majority carriers) flow from S to D whereas conventional drain current I<sub>D</sub> flows through the channel from D to S.

Fig. 6 JFET at  $V_{GS} = 0V$  and  $V_{DS} > 0V$

- Since the p region of an n-channel JFET is heavily doped, as compared to the n-channel, the depletion region extends less into the p region and deeper into the n-channel as shown in Fig. 6.

- It is important to note that the depletion region penetrates more deeply into the n-channel near the drain terminal and less near the source terminal.

- This is because the channel has some finite resistance, it will cause some voltage drop across the channel. The voltage drop nearer to the drain terminal is more compared to source terminal, due to this reverse bias voltage is higher near the drain end of the channel as compared to the source end. So the depletion region extends more deeply into the n-channel near the drain terminal.

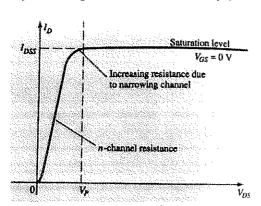

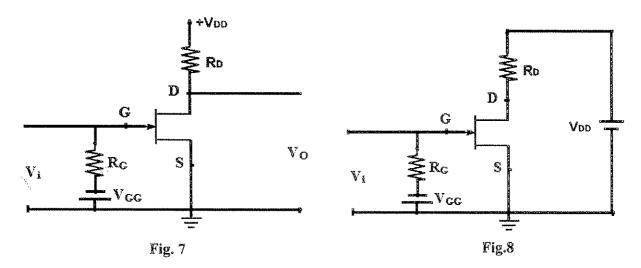

Fig. 7  $I_D$  versus  $V_{DS}$  for  $V_{GS}$ =0V

Fig. 8

- As the voltage V<sub>DS</sub> is increased from zero, the current I<sub>D</sub> in channel increases according to ohm's law as shown in Fig. 7.

- As V<sub>DS</sub> increases, the depletion regions widens, causing a noticable reduction in the channel width. The reduced path of conduction causes the resistance to increase and the drain current I<sub>D</sub> reaches saturation because of this.

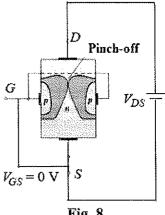

- If  $V_{DS}$  is increased to a level where two depletion regions will "touch" each other as shown in Fig. 8, is known as pinch-off. The level of  $V_{DS}$  that establishes this condition is referred to as the pinch-off *voltage* and is denoted by  $V_P$  as shown in Fig. 7.

Fig. 9

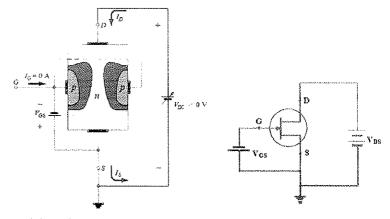

- After pinch-off voltage, the channel width becomes so narrow (very less) that depletion layers almost touch each other (shown in Fig. 9). The drain current passes through the small passage between these layers. Therefore I<sub>D</sub> remains constant, when V<sub>DS</sub> is increased beyond V<sub>P</sub>.

- The current flow from drain to source when  $V_{DS} > V_P$  &  $V_{GS} = 0V$  is known as drain to source current with a short circuit from gate to source & it is denoted by loss.

- $I_{DSS}$  is the maximum drain current for a JFET & is defined by conditions  $V_{DS} > V_P$  &  $V_{GS} = 0V$ .

- I<sub>DSS</sub> = Drain to Source current when the gate & source terminals are short circuited.

#### (3) When $V_{GS} \le 0V$ (that means negative voltage, $V_{GS} = -ve$ ) and $V_{DS} > 0$

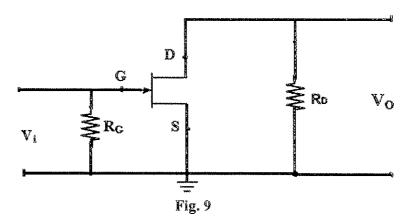

- Negative voltage is applied between gate and source of FET as shown in Fig. 10.

- The effect of the applied negative bias is to establish depletion regions similar to those obtained with V<sub>GS</sub> = 0V, but at lower levels of V<sub>DS</sub>.

- Therefore, the result of applying a negative bias to the gate is to reach saturation level at a lower level of V<sub>DS</sub> as shown in Fig. 11.

${f Fig.~10}$  Application of a negative voltage to the gate of a JFET

• The resulting saturation level for I<sub>D</sub> has been reduced and in fact will continue to decrease as V<sub>GS</sub> is made more & more negative. (as shown in Fig. 11)

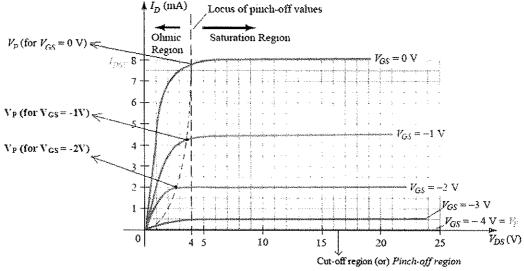

Fig. 11 n-channel JFET characteristics with  $I_{DSS} = 8mA \& V_P = -4V$

- When  $V_{GS}$  is sufficiently negative where drain current  $I_D = 0$  mA, the device is "turned-off". At this point  $V_{GS} = -V_P$ . (device is in cut-off region)

- The level of  $V_{GS}$  that results in  $I_D = 0$  mA is defined as  $V_{GS} = -V_P$  for n-channel ( $V_{GS} = +V_P$  for p-channel JFET).

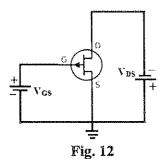

**NOTE:** The working of p-channel JFET is exactly similar to that of n-channel JFET except that the current carriers are holes and polarities of both the voltage sources  $V_{GS}$  &  $V_{DS}$  are reversed. It means that  $V_{GS}$  would be positive for a p-channel JFET and  $V_{DS}$  is negative as shown in Fig. 12. Here, Drain terminal is connected to negative and Source is connected to positive terminal of the battery.

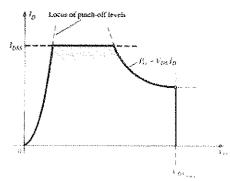

## 3.7 Output characteristics (Drain characteristics) of n- channel JFET:

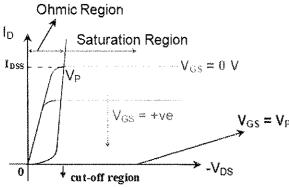

The graph of drain current ( $I_D$ ) versus drain-to-source voltage ( $V_{DS}$ ) at constant gate-to-source voltage ( $V_{GS}$ ) is termed as drain characteristics or output characteristics.

Drain characteristics of n-channel JFET is shown in Fig. 11 and has been already discussed in the section 3.6.1. It can be subdivided into three regions:

## 1) Ohmic region: (For $V_{DS} > 0$ and $V_{DS} < V_P$ )

The region to the left of the pinch-off locus of Fig. 11 is referred to as the ohmic region. For lower values of  $V_{DS}$  depletion layer of the channel is very small and the JFET acts like a voltage controlled resistor and the curve is almost linear. That means as the voltage  $V_{DS}$  is incressed from zero, the current  $I_D$  also increases proportionally according to ohms law ( $I \propto V$ ). So this region is called ohmic region.

#### 2) Saturation region:

After pinch-off voltage, the channel width becomes so narrow (very small) that depletion layers almost touch each other. The drain current  $I_D$  passes through the small passage between these layers. Therefore, increase in drain current is very small with  $V_{DS}$  above pinch-off voltage. Consequently drain current remains constant.

From Fig. 13, It is seen that with  $V_{GS} = 0$ ,  $I_D$  saturates at  $I_{DSS}$  and the characteristic shows  $V_{DS} = 4V$ . When an external bias of  $V_{GS} = -1$  V is applied,  $I_D$  saturates at  $V_{DS} = 3V$ . (The effect of the applied negative bias is to establish depletion regions similar to those obtained with  $V_{GS} = 0V$ , but at lower levels of  $V_{DS}$ ) Similarly when  $V_{GS} = -2V$ ,  $I_D$  saturates at  $V_{DS} = 2V$  and so on.

Therefore, the result of applying a negative bias to the gate is to reach saturation level at a lower level of V<sub>DS</sub> as shown in Fig. 11 & Fig. 13.

Since,  $I_D$  remains constant (saturates) irrespective of the rise in voltage  $V_{DS}$  this region is called saturation region.

#### 3) Cut-off region:

As  $V_{GS}$  is made more negative for any value of  $V_{DS}$ , effective channel width decreases and at a certain value of  $V_{GS} = V_P$ , the channel is completely pinched-off (completely block) reducing  $I_D$  to zero for all values of  $V_{DS}$ .

For a gate-to-source voltage  $V_{GS}$  less than (more negative than) the pinch-off level, the drain current is Zero ( $I_D = 0A$ ) as shown in Fig. 11 is called cut-off region.

| Region            | Function of JFET |        |  |

|-------------------|------------------|--------|--|

| Saturation region | Amplifie         | r      |  |

| Cut-off region    | Open switch      | 0.4.7  |  |

| Ohmic region      | Closed switch    | Switch |  |

Fig. 14 drain characteristics of P-JFET

Note: Typical p-channel JFET drain characteristics are shown in Fig. 14. It is seen that these are similar to the characteristics for an n-channel JFET, except for the voltage polarities ( $V_{DS}$  is negative). Here also when  $V_{GS} = 0 V$ ,  $I_D$  reaches its maximum value that is  $I_{DSS}$  and progressively more positive levels of  $V_{GS}$  reduce  $I_D$  towards cut-off region.

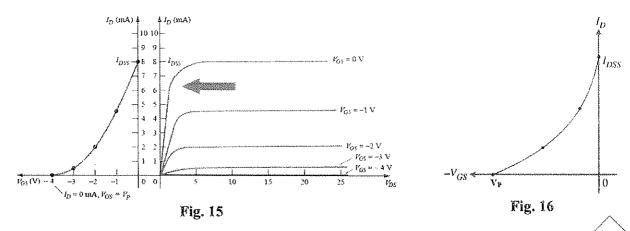

## 3.8 Transfer Characteristics of n- channel JFET:

• For the BJT transistor the output current  $I_C$  and input controlling current  $I_B$  were related by beta, which was considered constant for the analysis to be performed. In equation form,

control variable

$$I_C = f(I_B) = \beta I_B$$

constant

- In Eq. (1) a linear relationship exists between  $I_C$  and  $I_B$ . Double the level of  $I_B$  and  $I_C$  will also doubles. Unfortunately, this linear relationship does not exist between the output and input quantities of a JFET.

- Transfer characteristics are the plot of  $I_D$  against the variations of  $V_{GS}$ . There is a non-linear relationship exist between  $I_D$  &  $V_{GS}$ . The relationship between  $I_D$  &  $V_{GS}$  is defined by Shockley and that equation is known as **Shockley's equation**:

$$I_D = I_{DSS} \left(1 - \frac{V_{GS}}{V_p}\right)^2$$

control variable constants (2)

Where, IDSS is drain to source current when gate & source are short circuited VP is pinch-off voltage

Vos is voltage between gate & source

- In Eq. (2) I<sub>DSS</sub> & V<sub>P</sub> are constant, where as V<sub>GS</sub> is control variable.

- The transfer characteristics defined by Shockley's equation are unaffected by the network in which the device is employed.

The transfer curve can be obtained using Shockley's equation or from the output characteristics.

From Eq. (2):

When

$$V_{GS} = 0$$

V,  $I_D = I_{DSS} \left[ 1 - \frac{0}{V_P} \right]^2$ ,  $I_D = I_{DSS} [1 - 0]^2$

Therefore,

$$I_D = I_{DSS}$$

When  $V_{GS} = V_P$ ,  $I_D = I_{DSS} \left[ 1 - \frac{V_P}{V_P} \right]^2$ ,  $I_D = I_{DSS} [1 - 1]^2$

Therefore,

By using these two data, the transfer characteristics have been plotted that is shown in Fig. 15 & Fig.16. From Eq. (2):

•

$$\frac{I_{D}}{I_{DSS}} = \left[1 - \frac{V_{GS}}{V_{P}}\right]^{2}$$

•

$$\left[1 - \frac{V_{GS}}{V_{P}}\right] = \sqrt{\frac{I_{D}}{I_{DSS}}}$$

•

$$\frac{V_{GS}}{V_{P}} = 1 - \sqrt{\frac{I_{D}}{I_{DSS}}}$$

•

$$V_{GS} = V_{P}\left[1 - \sqrt{\frac{I_{D}}{I_{DSS}}}\right] - - - \rightarrow (3)$$

• On most of the specification sheets the pinch-off voltage is specified as V<sub>GS(off)</sub> rather than V<sub>P</sub>. Therefore Eq. (2) becomes

$$\left| \mathbf{I}_{D} = \mathbf{I}_{DSS} \left[ \mathbf{1} - \frac{\mathbf{v}_{GS}}{\mathbf{v}_{GS(off)}} \right]^{2} \right| - - - - - \blacktriangleright (4)$$

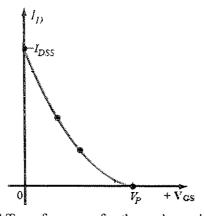

Note: For p-channel JFET Shockley's Eq. 2 can still be applied exactly as it appears. In this case, both  $V_P$  and  $V_{GS}$  will be positive as shown in Fig. 17 and the curve will be the mirror image of the transfer curve obtained with an n-channel.

Fig. 17 Transfer curve for the p-channel JFET

## 3.9 Specification Sheets of JFETs:

Although the general content of specification sheets may vary from the absolute minimum to an extensive display of graphs and charts, there are a few fundamental parameters that will be provided by all manufacturers. A few of the most important are discussed in the following paragraphs. The specification sheet for the 2N5457 *n*-channel JFET as provided by Motorola is provided in Fig. 18.

|  | <b>MAXIMUM</b> | RATINGS |

|--|----------------|---------|

|--|----------------|---------|

| Rating                                                                | Symbol            | Value       | Unit        |

|-----------------------------------------------------------------------|-------------------|-------------|-------------|

| Drain-Source Voltage                                                  | ∀ps               | 25          | Vde         |

| Drain-Gete Voltage                                                    | VDG               | 25          | Vd¢         |

| Reverse Gate - Source Voltage                                         | V <sub>G</sub> sR | ~25         | Vdc         |

| Gate Current                                                          | lG                | 10          | mAdc        |

| Total Device Dissipation @ T <sub>A</sub> = 25°C<br>Derate above 25°C | PD                | 310<br>2.82 | mW<br>mW/°C |

| Junction Temperature Range                                            | TJ                | 125         | °C          |

| Storage Channel Temperature Range                                     | Υstg              | ~65 to +150 | °C          |

Fig. 18

## 3.9.1 Maximum Ratings

- The maximum rating list usually appears at the beginning of the specification sheet, with the maximum voltages between specific terminals, maximum current levels, and the maximum power dissipation level of the device.

- The specified maximum levels for V<sub>DS</sub> and V<sub>DG</sub> must not be exceeded at any point in the design of the device.

- The applied source V<sub>DD</sub> can exceed these levels, but the actual level of voltage between these terminals must never exceed the level specified. Any good design will try to avoid these levels by a good margin of safety.

- The term reverse in V<sub>GSR</sub> defines the maximum voltage with the source positive with respect to the gate (as normally biased for an *n*-channel device) before breakdown will occur.

- On some specification sheets it is referred to as  $BV_{DSS}$  the Breakdown Voltage with the Drain-Source Shorted ( $V_{DS} = 0$  V). Although normally designed to operate with  $I_G = 0$  mA, if forced to accept a gate current, it could withstand 10 mA before damage would occur.

- The total device dissipation at 25°C (room temperature) is the maximum power the device can dissipate under normal operating conditions and is defined by

$$P_D = V_{DS} I_{D}$$

• Gate-source cut-off voltage V<sub>GS(off)</sub> = V<sub>P</sub> is nothing but pinch-off voltage. Another parameter is I<sub>DSS</sub> (drain to source current with V<sub>GS</sub>=0V) indicated on sheet. This is mentioned in the data sheet between minimum value & maximum value.

# 3.9.2 Operating Region

- The specification sheet and the curve defined by the pinch-off levels at each level of V<sub>GS</sub> define the region of operation for linear amplification on the drain characteristics as shown in Fig. 19.

- The ohmic region defines the minimum permissible values of  $V_{DS}$  at each level of  $V_{GS}$ , and  $V_{DSmax}$  specifies the maximum value for this parameter.

- The saturation current I<sub>DSS</sub> is the maximum drain current, and the maximum power dissipation level shown gives the limitation on the power dissipation in the device.

- The resulting shaded region is the normal operating region for amplifier design.

Fig. 19

$$JFET \qquad BJT$$

$$I_D = I_{DSS} \left(1 - \frac{V_{GS}}{V_P}\right)^2 \Leftrightarrow I_C = \beta I_B$$

$$I_D = I_S \qquad \Leftrightarrow \qquad I_C \cong I_E$$

$$I_G \cong 0 \text{ A} \qquad \Leftrightarrow \qquad V_{BE} \cong 0.7 \text{ V}$$

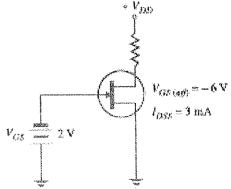

**Example 3.1** Determine the value of drain current for the circuit shown below.

Given:

$$V_{GS} = -2V$$

,  $V_{GS(off)} = -6V = V_P$ ,  $I_{DSS} = 3mA$

Therefore,

$$I_D = I_{DSS} \left[ 1 - \frac{v_{GS}}{v_P} \right]^2$$

$$I_D = (3 \text{ mA}) \left[ \left[ 1 - \frac{-2}{-6} \right]^2 \right]$$

**Example 3.2** A JFET has the following parameters:  $I_{DSS} = 32mA$ ,  $V_{GS(off)} = -8V & V_{GS} = -4.5 V$ . Find the value of drain current. Solution:

$$I_{D} = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_{P}} \right]^{2}$$

$$I_{D} = (32 \text{ mA}) \left[ \left[ 1 - \frac{-4.5}{-8} \right]^{2} \right]$$

$$I_{D} = 6.12 \text{mA}$$

# 3.10 Biasing of n - channel JFET

To use a FET in any application, (as a switch or as an amplifier) it is necessary first to bias the device. The usual reason for this biasing is to turn the device ON and operate the FET in a particular region (Saturation region or ohmic region or cut-off region) depending on the particular application.

The general relationships that can be applied to the dc analysis of all FET amplifiers are:

$$I_{\mathcal{G}} \cong 0 \text{ A} \qquad \text{and}$$

$$I_{\mathcal{D}} = I_{\mathcal{S}}$$

For JFETS, Shockley's equation is applied to relate the input and output quantities:

$$I_D = I_{DSS} \left(\frac{1 - V_{GS}}{V_P}\right)^2$$

# 3.11 Fixed-Bias Configuration (Gate Bias Configuration) for n- JFET:

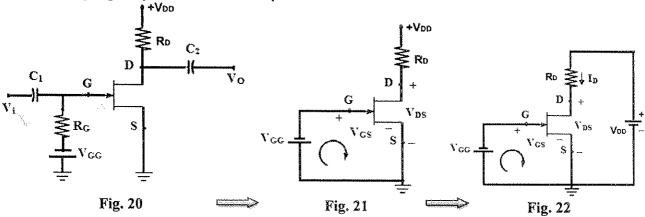

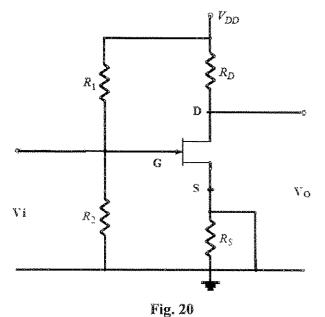

- The simplest of biasing arrangement for the n-channel JFET is as shown in Fig. 20, known as fixed bias configuration.

- For AC analysis coupling capacitors  $C_1$  &  $C_2$  offers very low impedance and for DC analysis they offer very high impedance. Therefore open circuit  $C_1$  &  $C_2$ .

- The gate resistance R<sub>G</sub> is necessary only to isolate an AC signal.

- For the dc analysis,

$$I_G = 0 A$$

Therefore, the voltage drop across resistance

$$V_{RG} = I_G R_G$$

$$V_{RG} = (0)R_G$$

$$V_{RG} = 0 V$$

- Therefore R<sub>G</sub> is replaced by short-circuit for dc analysis. (shown in Fig. 21)

- Apply KVL to input loop of Fig. 21

$$-V_{GG} - V_{GS} = 0$$

$V_{GS} = -V_{GG}$  ----> (5)

- This biasing method is called fixed bias because the gate-to-source voltage  $(V_{GS})$  is fixed by the constant voltage  $V_{GG}$ .

- The network shown in Fig. 21 can be replaced by Fig. 22.

- Apply KVL to output loop of Fig. 22

$$V_{DD} - I_{D}R_{D} - V_{DS} = 0$$

$V_{DS} = V_{DD} - I_{D}R_{D}$  ---- (6)

• The drain current ( $I_D$ ) corresponding to  $V_{DS}$  of Eq. (2) can be obtained by Shockley's equation:

$$I_{\rm D} = I_{\rm DSS} \Big[ 1 - \frac{V_{\rm GS}}{V_{\rm P}} \Big]^2$$

#### Merits:

- Simple biasing circuit.

- Analysis is simple.

- Design is simple.

#### **Demerits:**

- Requires two DC supplies (V<sub>DD</sub> & V<sub>GG</sub>), hence its use is limited.

- Thermally not stable.

- Fails to maintain the stability of Q point (operating point) against temperature & device parameter variations.

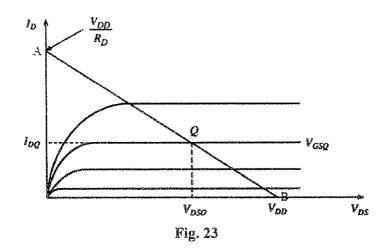

### 3.11.1 DC Load Line:

Consider Eq. (6),

$$V_{DS} = V_{DD} - I_D R_D$$

From the above equation we know that,

When,  $I_D = 0$ ,

$V_{DS} = V_{DD}$  (The load line intersects the  $V_{DS}$  axis at  $V_{DD}$ ) we get a point B on X-axis When,  $V_{DS} = 0$ ,

$I_D = \frac{V_{DD}}{R_D}$  (The load line intersects the  $I_D$  axis at  $V_{DD}/R_D$ ) we get a point A on Y-axis

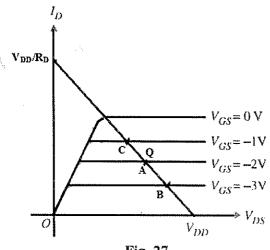

The Fig. 23 shows the output characteristics of the n-channel JFET with points A & B, and line drawn between them. The line drawn between points A & B is called DC load line. The intersection of curves of different values of V<sub>GS</sub> with DC load line gives operating point or Q-point.

The Q - point is generally situated at the middle point of the load line so that

$$V_{DSQ} = \frac{V_{DD}}{2}$$

and  $I_{DQ} = \frac{I_{DSS}}{2}$

# 3.11.2 Analysis of fixed bias circuit:

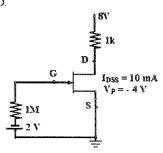

Example 3.3 For the circuit shown in the figure, calculate VGSQ, IDQ, VDSQ & VD

Solution:

From Eq. 5,

V<sub>GSO</sub> = - V<sub>GG</sub> = - 2V

From Eq. 2,

•

$$I_{DQ} = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_P} \right]^2$$

$I_{DQ} = (10 \times 10^{-3}) \left[ 1 - \frac{-2}{-4} \right]^2$

$I_{DQ} = 2.5 \text{ mA}$

From Eq. 6.

•

$$V_{DSQ} = V_{DD} - I_D R_D$$

$V_{DSQ} = 8 - [(2.5 \times 10^{-3}) \times (1 \times 10^3)]$

$V_{DSQ} = 5.5 V$

Given:  $R_D = 1 k\Omega$  $V_{DD} = 8V$  $R_G = 1M\Omega$  $V_{GG} = 2V$  $I_{DSS} = 10 \text{ mA}$  $V_P = -4V$

$V_{DS} = V_D - V_S$ Here,  $V_S = 0$  (since source is directly connected to ground)  $\overline{V_{DS}} = V_D = 5.5 \text{ V}$

Example 3.4 For the circuit shown in the figure, calculate V<sub>GSQ</sub>, I<sub>DQ</sub>, V<sub>DSQ</sub>, V<sub>S</sub>, V<sub>G</sub> & V<sub>D</sub>.

Solution:

From Eq. 5,

•

$$V_{GSO} = -V_{GG} = -2V$$

From Eq. 2,

•

$$I_{DQ} = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_P} \right]^2$$

$$I_{DQ} = (10 \times 10^{-3}) \left[ 1 - \frac{-2}{-8} \right]^2$$

$$I_{DQ} = 5.625 \text{ mA}$$

From Eq.6,

•

$$V_{DSQ} = V_{DD} - I_D R_D$$

$V_{DSQ} = 16 - [(5.625 \times 10^{-3}) \times (2 \times 10^{3})]$

$\boxed{V_{DSQ} = 4.75 \text{ V}}$

Given:  $R_D = 2 k\Omega$  $V_{DD} = 16V$  $R_G = 1M\Omega$  $V_{GG} = 2V$

$$I_{DSS} = 10 \text{ mA}$$

$$V_P = -8V$$

$V_{DS} = V_D - V_S$ Here,  $V_S = 0$  (since source is directly connected to ground)

$$V_{DS} = V_D = 4.75 \text{ V}$$

$$V_{GS} = V_G - V_S$$

$$V_{GS} = V_G - 0$$

$$V_{GS} = V_G = 2V$$

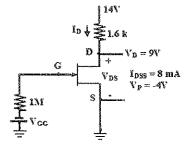

**Example 3.5** For the circuit shown in the figure, Find: V<sub>DS.</sub> I<sub>D</sub> & V<sub>GG.</sub>

Solution:

$V_{DS} = V_D - V_S$ Here,  $V_S = 0$  (since source is directly connected to ground)  $V_{DS} = V_D = 9 V$

From Eq.6,

•

$$V_{DS} = V_{DD} - I_D R_D$$

$I_D = \left[ \frac{(V_{DD} - V_{DS})}{R_D} \right] = \left[ \frac{14 - 9}{1.6 \times 10^3} \right] = 3.125 \text{ mA}$

$$I_D = 3.125 \text{ mA}$$

We know that, From Eq.3,

•

$$V_{GS} = V_P \left[ 1 - \sqrt{\frac{I_D}{I_{DSS}}} \right]$$

Given:  $R_D = 1.6 k\Omega$  $V_{DD} = 14V$

$$R_G = 1M\Omega$$

$$V_D = 9V$$

$$I_{DSS} = 8 \text{ mA}$$

$V_P = -4V$

•  $V_{GS} = -4 \left[ 1 - \sqrt{\frac{3.125 \times 10^{-3}}{8 \times 10^{-3}}} \right]$

$$\begin{bmatrix} V_{GS} = -1.5 \text{ V} \\ \text{From Eq. 5,} \\ V_{GG} = -V_{GS} = 1.5 \text{ V} \end{bmatrix}$$

## 3.12 Self-Bias Configuration:

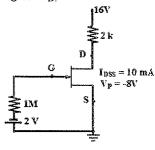

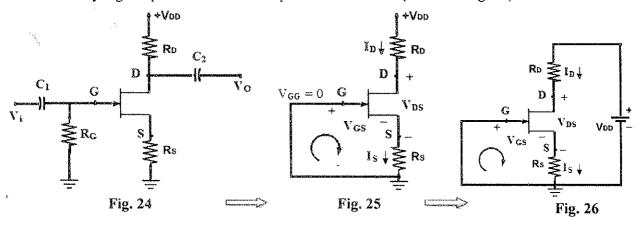

- The self-bias configuration eliminates the need of two separate DC supplies. Self-bias is the most common type of biasing circuit used to bias the JFET, because it requires single DC supply for biasing (shown in Fig. 24).

- The condition required to bias the n channel JFET is the gate-source voltage  $V_{GS}$  must be reverse biased. That is  $V_{GS}$  is negative.

- The condition required to bias the p channel JFET is the gate-source voltage  $V_{GS}$  must be reverse biased. That is  $V_{GS}$  is positive.

- For AC analysis coupling capacitors C<sub>1</sub> & C<sub>2</sub> offers very low impedance and for DC analysis they offer very high impedance. Therefore open circuit C<sub>1</sub> & C<sub>2</sub> (shown in Fig. 25).

- The gate Resistance R<sub>G</sub> is necessary only to isolate an AC signal.

- For the dc analysis,

$$l_G \cong 0 A$$

Therefore, the voltage drop across resistance

$$R_G$$

is:  $V_{RG} = I_G R_G$

$V_{RG} = (0)R_G$

$V_{RG} = 0 V$

- Therefore R<sub>G</sub> is replaced by short-circuit for the dc analysis. (shown in Fig. 25)

- The network shown in Fig. 25 can be replaced by Fig. 26.

- From the Fig. 26 it is observed that  $I_D \cong I_S$

- Apply KVL to input loop of Fig. 26  $-V_{GS} I_{D}R_{S} = 0$   $\boxed{V_{GS} = -I_{D}R_{S}} - - \rightarrow (7)$

- Eq. (7) indicates that gate-source voltage V<sub>GS</sub> is negative because of voltage drop across R<sub>S</sub>.

- The voltage drop across Rs makes gate-source junction reverse biased.

- Apply KVL to output loop of Fig. 26  $V_{DD} I_D R_D V_{DS} I_D R_S = 0$ But  $I_D = I_S$   $V_{DD} I_D (R_D + R_S) V_{DS} = 0$   $\boxed{V_{DS} = V_{DD} I_D (R_D + R_S)} --- \blacktriangleright (8)$

- Shockley's equation relating input & output quantities:

$$I_{D} = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_{P}} \right]^{2}$$

#### Merits:

- Requires only one DC supply (V<sub>DD</sub>) for biasing.

- Operating point (Q point) is stable against temperature variations & device parameter variations.

## How resistance Rs does provide the stability against temperature & device parameter variations?

- In self bias circuit the required V<sub>GS</sub> can be provided through voltage drop across resistance R<sub>S</sub>.

- That is,  $V_{GS} = -I_D R_S$  (from Eq. 7)

- When **Temperature** increases In increases (because of increase in temperature more number of electrons get generated in the channel which intern increase the current I<sub>D</sub>)

- When In increases

IDRs increases (the potential drop across Rs increases)

Fig. 27

- That is, V<sub>GS</sub> = I<sub>D</sub>Rs increases. (Here, the Q point depends on V<sub>GS</sub>, this increase in V<sub>GS</sub> causes the Q point to shift from its original position, i.e., from point A to point B, it is illustrated in Fig. 27)

- As V<sub>GS</sub> increases, this makes V<sub>GS</sub> more & more negative. Due to this the channel width decreases because the depletion region increases and hence In decreases. (this decrease in I<sub>D</sub> brings the Q point to its original position, i.e., from point B to point A)

- This offsets (compensates) the initial increase in I<sub>D</sub>.

- From the above discussion it is clear that the increasing tendency of I<sub>D</sub> (due to rise in temperature) decreases itself. In other words there is a feedback mechanism which tends to keep I<sub>D</sub> stable. So Q point remains stable in self bias circuit.

Similarly,

When temperature decreases

V<sub>GS</sub> = - I<sub>D</sub>Rs decreases

(This decreases in V<sub>GS</sub>)

(This decrease in  $V_{GS}$  causes the Q point to shift from its original position, i.e., from point A to point C, it is illustrated in Fig. 27)

When VGs decreases — In increases

(As  $V_{GS}$  decreases, this makes  $V_{GS}$  less negative. Due to this the channel width increases because the depletion region decreases and hence  $I_D$  increases.

When In increases — This offsets (compensates) the initial decrease in I<sub>D</sub>. (This increase in I<sub>D</sub> brings the Q point to its original position, i.e., from point C to point A)

This is how the resistance R<sub>S</sub> maintains the stability of the Q point against temperature variations, that's why this biasing circuit is called Self bias circuit.

## 3.12.1 Analysis of Self bias circuit:

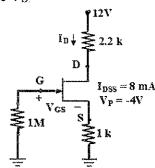

**Example 3.6** For the circuit shown in the figure, calculate I<sub>DQ</sub>, V<sub>GSQ</sub>, V<sub>DSQ</sub>, V<sub>S</sub> & V<sub>D</sub> Solution: From Eq. 7,

$\bullet V_{GS} = -I_D R_S$

From Eq. 2,

$$I_{D} = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_{P}} \right]^{2} \text{, therefore}$$

$$I_{D} = I_{DSS} \left[ 1 - \frac{(-I_{D} R_{S})}{V_{P}} \right]^{2}$$

$$I_{D} = (8 \times 10^{-3}) \left[ 1 - \frac{(-I_{D} \times 1 \times 10^{3})}{-4} \right]^{2}$$

$$I_{DQ} = 2 \text{ mA}$$

Given:  $V_{DD} = 12V$  $R_D = 2.2 \text{ k}\Omega$  $R_G = 1M\Omega$  $R_S = 1 k\Omega$  $I_{DSS} = 8 \ mA$

Therefore,

•

$$V_{GS} = -I_D R_S$$

$V_{GS} = -(2 \times 10^{-3} \times 1 \times 10^3)$

$V_{GSQ} = -2 V$

From Eq. 8,

•

$$V_{DS} = V_{DD} - I_D (R_D + R_S)$$

$V_{DS} = 12 - (2 \times 10^{-3})[(2.2 \times 10^3) + (1 \times 10^3)]$

$V_{DSQ} = 5.6 \text{ V}$

•

$$V_S = I_D R_S$$

$V_S = (2 \times 10^{-3}) (1 \times 10^3)$

$V_S = 2 \text{ V}$

$$V_{DS} = V_{D} - V_{S}$$

$$V_{D} = V_{DS} + V_{S}$$

$$V_{D} = 5.6 + 2$$

$$V_{D} = 7.6 \text{ V}$$

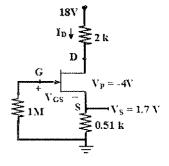

Example 3.7 Given  $V_S = 1.7 \text{ V}$  for the network of figure below. Find  $I_{DQ}$ ,  $V_{GSQ}$ ,  $I_{DSS}$ ,  $V_D$  &  $V_{DS}$ . Solution: We know that,

•

$$V_S = I_D R_S$$

$I_D = \frac{V_S}{R_S} = \frac{1.7}{0.51 \times 10^3} = 3.34 \text{ mA}$

Given:

$$V_{DD} = 18V$$

$R_D = 2 k\Omega$

$R_G = 1M\Omega$

$R_S = 0.51 k\Omega$

$V_P = -4V$

From Eq. 7,

$$V_{GS} = -I_{D}R_{S}$$

$$V_{GS} = -(3.34 \times 10^{-3} \times 0.51 \times 10^{3})$$

$$V_{GSQ} = -1.7 \text{ V}$$

From Eq. 2,

Therefore,

$$\frac{(3.34 \times 10^{-3}) = I_{DSS} \left[1 - \frac{(-1.7)}{-4}\right]^2}{I_{DSS} = 10.11 \text{ mA}}$$

From Eq. 8,

- $V_{DS} = V_{DD} I_D (R_D + R_S)$   $V_{DS} = 18 - (3.34 \times 10^{-3})[(2 \times 10^3) + (0.51 \times 10^3)]$  $V_{DS} = 9.62 \text{ V}$

- $V_{DS} = V_D V_S$   $V_D = V_{DS} + V_S$   $V_D = 9.62 + 1.7$  $V_D = 11.32 \text{ V}$

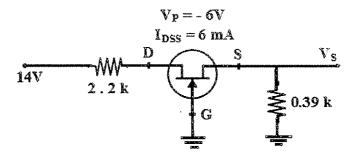

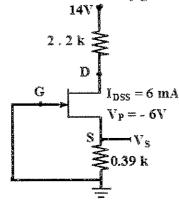

#### Example 3.8 Find V<sub>S</sub> for the circuit shown in figure.

Solution:

The given circuit is redrawn as shown in the figure below

Given  $\begin{aligned} &V_{DD}=14V\\ &R_D=2.2\ k\Omega\\ &R_S=0.39\ k\Omega\\ &V_P=-6V \end{aligned}$

$I_{DSS} = 6 \text{ mA}$

From Eq. 7,

•

$$V_{GS} = -I_D R_S$$

$V_{GS} = -I_D \times (0.39 \times 10^3)$

From Eq. 2,

•

$$I_D = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_P} \right]^2$$

Therefore,

$$I_{D} = I_{DSS} \left[ 1 - \frac{(-I_{D} R_{S})}{V_{P}} \right]^{2}$$

$$I_{D} = (6 \times 10^{-3}) \left[ 1 - \frac{(-I_{D} \times 0.39 \times 10^{3})}{-6} \right]^{2}$$

$$I_{D} = 3.56 \text{ mA}$$

•

$$V_S = I_D R_S$$

$V_S = (3.56 \times 10^{-3}) (0.39 \times 10^3)$

$\boxed{V_S = 1.39 \text{ V}}$

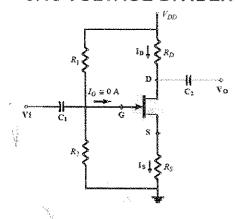

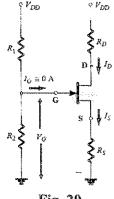

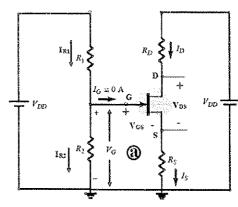

### 3.13 VOLTAGE-DIVIDER BIAS CONFIGURATION:

Fig. 28

- Fig. 28 shows the voltage divider bias circuit for n channel JFET.

- We know that Gate current,  $I_G = 0$  for JFET.

- For DC analysis network of Fig. 28 can be redrawn as shown in Fig. 29 & Fig. 30. Here, coupling capacitors are replaced by open circuit.

- V<sub>DD</sub> can be treated as separate two sources.

- Here, from Fig. 30

$$I_{R1} = I_{R2} + I_{G}$$

since

$$I_G = 0$$

$$I_{R1} = I_{R2}$$

- Same current is flowing through R<sub>1</sub> & R<sub>2</sub>, therefore they are in series.

- Here, V<sub>G</sub> is voltage between gate and ground.

- The voltage V<sub>G</sub> is given by

- $V_{R2} = V_G = I_{R2}R_2$

$$I_{RZ} = \frac{V_{DD}}{R_1 + R_2}$$

Therefore,

$$V_{G} = \frac{V_{DD} R_{2}}{R_{1} + R_{2}} - - - - - \rightarrow (9)$$

Fig. 29

Fig. 30

Apply KVL around loop a to the Fig. 30

$$V_G - V_{GS} - I_D R_S = 0$$

$V_{GS} = V_G - I_D R_S$  ----- (10)

Apply KVL around output loop of Fig. 30

$$V_{DD} - I_D R_D - V_{DS} - I_D R_S = 0$$

$$V_{DS} = V_{DD} - I_D(R_D + R_S)$$

(11)

Shockley's equation relating input and output quantities is:

$$I_{\rm D} = I_{\rm DSS} \left[ 1 - \frac{V_{\rm GS}}{V_{\rm P}} \right]^2$$

## 3.13.1 Analysis of Voltage-Divider Bias Configuration:

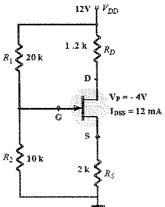

Example 3.9 For the circuit shown in the figure below, calculate  $V_G$ ,  $I_D$ ,  $V_{GS}$ ,  $V_{DS}$  &  $V_{S}$ .

Solution:

From Eq. 9,

•

$$V_G = \frac{V_{DD}R_2}{R_1 + R_2}$$

$V_G = \frac{12 \times 10 \times 10^3}{(20 \times 10^3) + (10 \times 10^3)}$

$V_G = 4V$

•

$$V_{GS} = V_G - I_D R_S$$

$V_{GS} = 4 - (I_D \times 2 \times 10^3)$

From Eq. 2,

•

$$I_D = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_P} \right]^2$$

.

Therefore,

$I_D = I_{DSS} \left[ 1 - \frac{(4 - I_D R_S)}{V_P} \right]^2$

$I_D = (12 \times 10^{-3}) \left[ 1 - \frac{(4 - (I_D \times 2 \times 10^3))}{-4} \right]^2$

$I_D = 3 \text{ mA}$

From Eq. 11,

•

$$V_{DS} = V_{DD} - I_D (R_D + R_S)$$

$V_{DS} = 12 - (3 \times 10^{-3})[(1.2 \times 10^3) + (2 \times 10^3)]$

$V_{DS} = 2.4 \text{ V}$

Therefore,

•

$$V_{GS} = V_G - I_D R_S$$

$V_{GS} = 4 - (3 \times 10^{-3} \times 2 \times 10^3)$

$V_{GS} = -2 V$

•

$$V_S = I_D R_S$$

$V_S = (3 \times 10^{-3}) (2 \times 10^3)$

$V_S = 6 V$

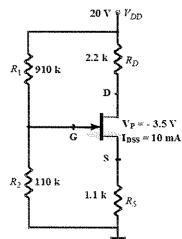

**Example 3.10** For the circuit shown in the figure below, calculate V<sub>G</sub>, I<sub>DQ</sub>, V<sub>GSQ</sub>, V<sub>D</sub>, V<sub>S</sub> & V<sub>DSQ</sub>. Solution:

From Eq. 9,

$$V_G = \frac{V_{DD}R_2}{R_1 + R_2}$$

$$V_G = \frac{20 \times 110 \times 10^3}{(910 \times 10^3) + (110 \times 10^3)}$$

•

$$V_{GS} = V_G - I_D R_S$$

$V_{GS} = 2.16 - (I_D \times 1.1 \times 10^3)$

$V_G = 2.16 \text{ V}$

From Eq. 2,

\*

$$I_D = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_P} \right]^2$$

,

Therefore,

$I_D = (10 \times 10^{-3}) \left[ 1 - \frac{(2.16 - (I_D \times 1.1 \times 10^3))}{-3.5} \right]^2$

$I_D = 3.32 \text{ mA}$

Therefore,

•

$$V_{GS} = V_G - I_D R_S$$

$V_{GS} = 2.16 - (3.32 \times 10^{-3} \times 1.1 \times 10^3)$

$V_{GS} = -1.492 \text{ V}$

From Eq. 11,

•

$$V_{DS} = V_{DD} - I_D (R_D + R_S)$$

$V_{DS} = 20 - (3.32 \times 10^{-3})[(2.2 \times 10^3) + (1.1 \times 10^3)]$

$V_{DS} = 9 \text{ V}$

•

$$V_S = I_D R_S$$

$V_S = (3.32 \times 10^{-3}) (1.1 \times 10^3)$

$V_S = 3.652 \text{ V}$

•

$$V_{DS} = V_D - V_S$$

Therefore,

$V_D = V_{DS} + V_S$

$V_D = 9 + 3.652$

$V_D = 12.652$  V

Given:

$$\begin{split} &V_{DD} = 20 \text{ V} \\ &V_{P} = -3.5 \text{ V} \\ &I_{DSS} = 10 \text{ mA} \\ &R_{1} = 910 \text{ k}\Omega \\ &R_{2} = 110 \text{ k}\Omega \\ &R_{D} = 2.2 \text{ k}\Omega \\ &R_{S} = 1.1 \text{ k}\Omega \end{split}$$

# **FET Small Signal Analysis**

#### 4.1 Introduction:

- Field-effect transistor (JFET) amplifiers provide an excellent voltage gain with the added feature of high input impedance. Because of their high input impedance and other characteristics features of JFETs, they are preferred over BJTs for certain types of applications.

- Whereas a BJT device controls a large output (collector) current by means of a relatively small input (base) current, the FET device controls an output (drain) current by means of a small input (gate-source voltage) voltage.

- In general, therefore, the BJT is a current-controlled device and the FET is a voltage-controlled device. In both cases, however, note that the output current is the controlled variable.

- Because of the high input characteristic of FETs, the ac equivalent model is somewhat simpler than that employed for BJTs. While the BJT had an amplification factor,  $\beta$  (beta), the FET has a transconductance factor,  $g_m$ .

- There are three terminals in a JFET viz., source, gate and drain. However, when JFET is to be connected in a circuit, we require four terminals; two for the input and two for the output. This difficulty is overcome by making one terminal of the JFET common to both input and output terminals.

- Accordingly, a JFET can be connected in a circuit in the following three ways (configurations):

- 1) Common source (CS) configuration

- 2) Common drain (CD) configuration

- 3) Common gate (CG) configuration

- The common source connection is the most widely used arrangement. It is because this connection provides high input impedance, good voltage gain and moderate output impedance. However, the circuit produces a phase reversal i.e., output signal is 180° out of phase with the input signal.

- A common source JFET amplifier is the JFET equivalent of common emitter amplifier. Both amplifiers have a 180° phase shift from input to output. Although the two amplifiers serve the same basic purpose, the means by which they operate are quite different.

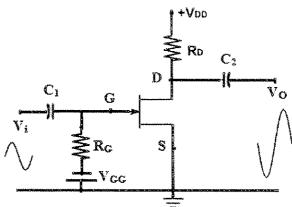

# 4.2 Basic CS configuration amplifier:

Fig. 1 common source circuit

- Fig.1 shows a common source n-channel JFET fixed bias amplifier. Note that source terminal is common to both input and output.

- In Fig.1, the voltage V<sub>GG</sub> provides the necessary reverse bias between gate and source of the JFET. The Input AC signal to be amplified is applied between gate and source through coupling capacitor C<sub>1</sub>.

V<sub>DD</sub> is another DC supply to bias drain and source. Output voltage V<sub>0</sub> can be obtained through another coupling capacitor C<sub>2</sub> between drain and source of JFET.

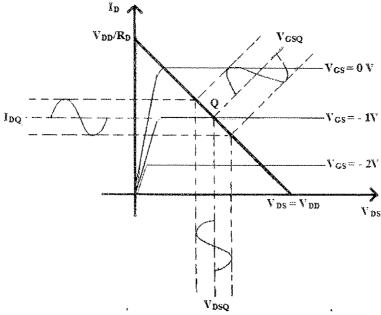

Fig. 2 Output characteristics of n-channel JFET

Drain characteristics of JFET is as shown in Fig. 2. Apply KVL to output circuit of Fig. 1

$$\begin{aligned} &V_{DS} = V_{DD} - I_D R_D & ----- > & (1) & (\text{Eq. 1 represents straight line}) \\ &\text{when,} & I_D = 0; & V_{DS} = V_{DD} & \text{point on X-axis} \\ &\text{when,} & V_{DS} = 0; & I_D = \frac{V_{DD}}{R_D} & \text{point on Y-axis} \end{aligned}$$

- Q-point is selected approximately at the midpoint of the load line. This gives undistorted output, i.e., output waveform is sinusoidal when the input signal applied is sinusoidal. This is valid when input signal is small at lower frequency and operating in the linear region.

- If the operating point is selected either close to the ohmic region or near the cut-off region that is at the one of the ends of the load line, the output sinusoidal would be clipped during either the positive or negative half-cycles of the input signal.

# 4.3 FET Small - Signal Model:

- The ac analysis of an FET configuration requires that a small-signal ac model for the FET. The gate to source voltage V<sub>GS</sub> controls the drain to source current I<sub>D</sub> of an FET.

The relationship between

$$V_{GS}$$

and  $I_D$  is given by Shockley's equation.

$$I_D = I_{DSS} \left[ 1 - \frac{v_{GS}}{v_P} \right]^2 - - - - - \rightarrow (2)$$

The drain current is controlled by the gate – source voltage (V<sub>GS</sub>).

i.e.,

$$I_D = f(V_{GS})$$

$I_D \propto V_{GS}$

$I_D = g_m V_{GS}$  ----- (3)

Here, g<sub>m</sub> is called the transconductance of FET.

$g_m$  is alternatively represented by  $y_{fs}$ , therefore,

$$g_{m} = y_{fs} \qquad ---- \qquad (4)$$

Here,  $y_{fs}$  is called forward transfer admittance.

## 4.3.1 Transconductance (g<sub>m</sub>):

- The transconductance gm of an FET can be defined as the change in drain current that will result from a change in gate to source voltage with drain to source voltage remains constant.

- $g_m = \frac{Change\ in\ I_D}{Change\ in\ V_{GS}}\ ,\ its\ unit\ is\ Siemens\ (S)\ or\ mho$

•

$$g_m = \frac{\Delta I_D}{\Delta V_{GS}}$$

--- • (5)

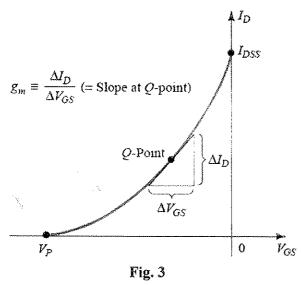

- Transconductance can be determined from transfer characteristics as shown in Fig. 3.

- Select Q point on the transfer characteristics and draw tangent at the Q point.

- Small change in drain current to small change in V<sub>GS</sub> about O point gives gm.

## Mathematical expression of g<sub>m</sub>:

Consider Eq. 2

$$I_D = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_P} \right]^2$$

---- (2)

- Where,  $|V_p|$  denotes magnitude only, to ensure positive value for  $g_m$ . Because,  $g_m$  is forward transfer admittance.

- When  $V_{GS} = 0$  V, the Eq. 6 becomes:

$$g_{m} = \frac{2I_{DSS}}{|V_{P}|} \left(1 - \frac{0}{V_{P}}\right)$$

$$g_{m0} = \frac{2I_{DSS}}{|V_{P}|} \qquad (7)$$

Where, added subscript 0 reminds us that it is the value of  $g_m$  when  $V_{GS} = 0V$ .

Therefore, Eq. 6 then becomes

$$\boxed{\mathbf{g_m} = \mathbf{g_{m\theta}}(1 - \frac{\mathbf{v_{GS}}}{\mathbf{v_p}})} \quad ---- \rightarrow \quad (8)$$

**Example 4.1** For JFET, if  $I_{DSS} = 10$  mA,  $V_P = -5V$  and  $g_{m0} = 4$ mS. Determine the transconductance for  $V_{GS} = -4V$  and find  $I_D$  at this point.

Solution: Given:

$$I_{DSS} = 10 \text{ mA}$$

$V_P = -5V$

$V_{GS} = -4V$

$g_{m0} = 4mS$

From Eq. 8

$$g_{m} = g_{m0}(1 - \frac{V_{GS}}{V_{P}})$$

$$g_{m} = (4 \times 10^{-3})(1 - \frac{-4}{-5})$$

$$g_{m} = 0.8 \text{ mS}$$

From Eq. 2

•

$$I_D = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_P} \right]^2$$

$I_D = (10 \times 10^{-3}) \left[ 1 - \frac{-4}{-5} \right]^2$

$I_D = 0.4 \text{ mA}$

**Example 4.2** For JFET, if  $I_{DSS}$ = 8 mA,  $V_P$ = -4V find: (a) The transconductance at  $V_{GS}$ = 0V

- - (b) The transconductance when  $V_{GS} = -0.5V$

- (c) Calculate drain current  $I_D$  at  $V_{GS} = -0.5V$

Solution:

Given:

$$I_{DSS} = 8 \text{ mA}$$

$V_P = -4V$

Transconductance at  $V_{GS} = 0V$  is  $g_{m0}$ Therefore, From Eq. 7

$$g_{m0} = \frac{2I_{DSS}}{|V_P|}$$

$$= \frac{2 \times 8 \times 10^{-3}}{4}$$

$$g_{m0} = 4 \text{ mS}$$

The transconductance when  $V_{GS} = -0.5V$  is

•

$$g_m = g_{m0}(1 - \frac{V_{GS}}{V_P})$$

$g_m = (4 \times 10^{-3})(1 - \frac{-0.5}{-4})$

$g_m = 3.5 \text{ mS}$

From Eq. 2

•

$$I_D = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_P} \right]^2$$

$I_D = (8 \times 10^{-3}) \left[ 1 - \frac{-0.5}{-4} \right]^2$

$I_D = 6.125 \text{ mA}$

# 4.3.2 FET input impedance Z<sub>i</sub>:

The input impedance of all commercially available FETs is sufficiently large. Therefore input terminals of FET can be treated as an open circuit.

Since

$$I_G = 0A$$

,

$$Z_i = \frac{V_i}{I_G} = \frac{V_i}{0}$$

$$Z_i = \infty$$

# 4.3.3 FET output impedance Zo:

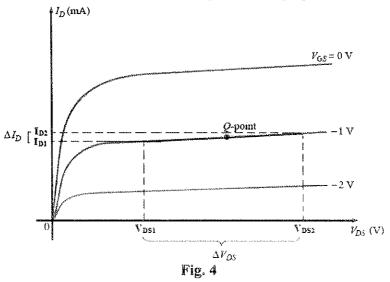

- Drain to source resistance (r<sub>d</sub>) is the resistance between the drain and source terminals when the JFET is operated in saturation region.

- It is the ratio of change in drain to source voltage ( $\Delta V_{DS}$ ) to the change in drain current ( $\Delta I_D$ ) at constant gate source voltage.

- ra resistance from drain to source Therefore,

$$r_d = \frac{v_{DS2} - v_{DS1}}{l_{D2} - l_{D1}}$$

$$r_d = \frac{\Delta v_{DS}}{\Delta l_{D}}$$

Output impedance of the FET is:

$$Z_0 = r_d$$

Since r<sub>d</sub> is usually the output resistance of a JFET it may also be expressed as output admittance y<sub>os</sub>.

(on FET specification sheet the output impedance will typically appear as admittance parameter y<sub>os</sub>)

y<sub>os</sub> admittance equivalent at output terminal with respect to source

$$\left( Z_0 = r_d = \frac{1}{y_{os}} \right) - \cdots \longrightarrow (9)$$

• Referring to the output characteristics of a JFET in Fig. 4 it is clear that above the pinch-off voltage, the change in  $I_D$  ( $I_{D1}$  to  $I_{D2}$ ) is small for a change in  $V_{DS}$  ( $V_{DS1}$  to  $V_{DS2}$ ) because the curve is almost flat. Therefore, drain resistance of a JFET has a large value ranging from 10 k $\Omega$  to 1 M $\Omega$ .

# 4.3.4 Amplification factor:

Amplification factor is the ratio of change in output voltage to the change in input voltage when drain current remains constant.

$$\mu = \frac{\Delta V_{DS}}{\Delta V_{GS}} \quad \text{at constant } I_D$$

$$\mu = \frac{\Delta V_{DS}}{\Delta I_D} \times \frac{\Delta I_D}{\Delta V_{GS}}$$

$$\mu = r_d g_m \qquad ---- \longrightarrow (10)$$

# 4.3.5 Impact of ID on gm:

• A mathematical relationship between g<sub>m</sub> and I<sub>D</sub> can be derived by noting that Shockley's equation can be written in the following form:

## 4.4 FET AC Equivalent Circuit:

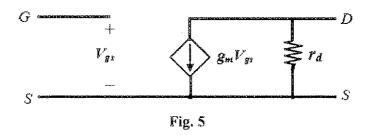

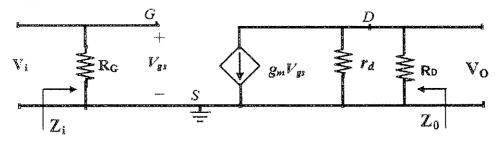

The small signal ac model of FET is required in the ac analysis of FET amplifiers. The small signal ac model is developed using the following facts.

- The input impedance between gate and source terminals of an FET is very high (since  $I_G = 0$ ). Therefore FET can be represented by an open circuit at the input terminal G and S.

- The output impedance is represented by the resistor  $r_d$  from drain to source.

- The control of I<sub>D</sub> by V<sub>gs</sub> is included as a current source g<sub>m</sub>V<sub>gs</sub> connected from drain to source as shown in Fig. 5.

- The current source g<sub>m</sub>V<sub>gs</sub> is voltage controlled that is controlled by input voltage V<sub>gs</sub> applied between input terminal G and S. The current source has its arrow pointing from drain to source to establish an 180° phase shift between output and input voltages.

- The lower case suffixes are used to imply that V<sub>gs</sub>, g<sub>m</sub> and r<sub>d</sub> are all ac values.

**Example 4.3** An FET has  $y_{fs}$ =3.8 mS and  $y_{os}$ = 20  $\mu$ S. Find  $g_m$  and  $r_d$  Solution:

•

$$g_m = y_{fs} = 3.8 \text{ mS}$$

•

$$r_d = \frac{1}{y_{os}} = \frac{1}{20 \times 10^{-6}}$$

$$r_d = 50 \text{ k}\Omega$$

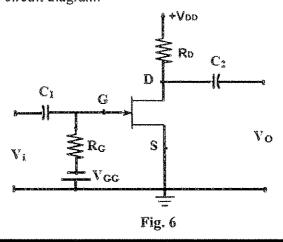

# 4.5 JFET Common Source Amplifier Using Fixed bias Configuration:

- The fixed bias CS amplifier with input voltage Vi applied through coupling capacitor C<sub>1</sub> and connected to output through another coupling capacitor C<sub>2</sub> is shown in Fig. 6.

- The analysis of JFET CS amplifier for its small signal behavior can be made by following simple guidelines:

Guide line 1: Draw the actual circuit diagram.

Guide line 2: Replace Coupling capacitors and bypass capacitor with short circuit. (Because the capacitors are selected in such a way that they should offer very less reactance to the AC)

Guide line 3: Replace all the DC sources ( $V_{DD}$  &  $V_{GG}$ ) with short circuit.

Guide line 4: Replace FET terminals Gate (G), Drain (D) and Source (S) with its equivalent circuit.

# 4.5.1 Input Impedance (Z<sub>i</sub>):

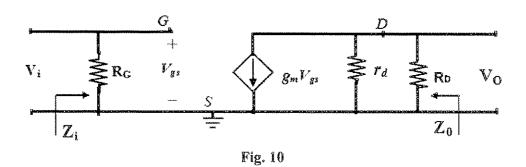

Fig. 10 clearly reveals that, there is an open circuit between the gate and source terminals; hence the input impedance is nothing but  $R_G$ . Therefore,

$$\overline{Z_i = R_G}$$

----- (12)

## 4.5.2 Output Impedance (Z₀):

- To find the output impedance we have to set Vi to zero.  $(V_i = 0)$

- From the Fig. 10 it is observed that  $V_i = V_{gs.}$

- Hence, with Vi = 0,  $g_mV_{gs} = 0$ .

- Thus the current source  $g_mV_{gs}$  is represented by an open circuit as shown in Fig. 11.

- From the circuit of Fig. 11, the output impedance  $Z_0$  is given by:

$$g_{m}V_{gs} = 0$$

$$Fig. 11$$

$$R_{0}$$

$$Z_{0}$$

$$Z_0 = r_d \mid \mid R_D \qquad (13)$$

$$Z_0 = \frac{R_D r_d}{r_d}$$

- If the resistance  $r_d$  is sufficiently large (at least 10:1) compared to  $R_D$ , (i.e.,  $r_d \ge 10R_D$ ), the approximation ( $r_d \mid \mid R_D$ )  $\approx R_D$  can often be applied.

- Therefore, Zo≈RD

## 4.5.3 Voltage gain (Av):

•

$$A_v = \frac{V_O}{V_i} = \frac{\text{output voltage}}{\text{input voltage}}$$

From Fig. 10

$$V_i = V_{gs}$$

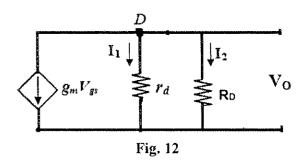

The output circuit of Fig. 10 is redrawn in Fig. 12 for convenience.

Apply KCL to node D, we have

Here,

$$g_m V_{gs} + I_1 + I_2 = 0$$

Here,  $I_1 = \frac{V_0}{r_d}$  and  $I_2 = \frac{V_0}{R_D}$

Therefore,  $g_m V_{gs} + \frac{V_0}{r_d} + \frac{V_0}{R_D} = 0$

•  $\frac{V_0}{r_d} + \frac{V_0}{R_D} = -g_m V_{gs}$

•  $V_0 \left[ \frac{1}{r_d} + \frac{1}{R_D} \right] = -g_m V_{gs}$

•  $V_0 = -g_m V_{gs} \left( \frac{r_d R_D}{r_d + R_D} \right)$

•  $V_0 = -g_m V_{gs} \left( \frac{r_d R_D}{r_d + R_D} \right)$

Therefore, •  $A_v = \frac{V_0}{V_i} = \frac{-g_m V_{gs} (r_d || R_D)}{V_{gs}}$

- The negative sign in the above equation clearly reveals a phase shift of 180° between input and output voltages.

- If  $r_d \ge 10 R_D$

$$\left( \mathbf{A}_{V} = -\mathbf{g}_{m} \mathbf{R}_{D} \right)$$

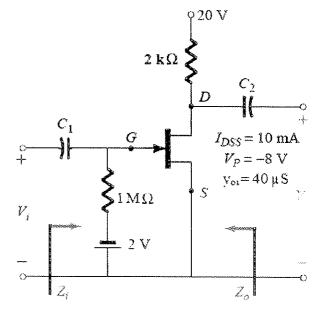

Example 4.4 For the FET amplifier shown below: Find gm, rd, Zi, Zo, Av and Av by ignoring the effect of rd.

Solution:

$$\label{eq:Given:RG} \begin{split} \text{Given:} & & R_G = 1 \text{ M}\Omega \\ V_{GG} = 2 \text{ V} & & R_D = 2 \text{ k}\Omega \\ I_{DQ} = 5.625 \text{ mA} & & V_{DD} = 20 \text{ V} \\ I_{DSS} = 10 \text{ mA} & & y_{os} = 40 \text{ }\mu\text{S} \\ V_P = -8 \text{ V} & & \end{split}$$

For fixed bias circuit, We know that:

$$V_{GS} = -V_{GG}$$

$$V_{GS} = -2 V$$

•

$$g_{m0} = \frac{2I_{DSS}}{|V_P|}$$

=  $\frac{2 \times 10 \times 10^{-3}}{8}$

$g_{m0} = 2.5 \text{ mS}$

$$g_{m} = g_{mo}(1 - \frac{V_{GS}}{V_{P}})$$

$$= (2.5 \times 10^{-3})(1 - \frac{-2}{-8})$$

$$g_{m} = 1.88 \text{ mS}$$

•

$$Z_0 = (r_d \mid \mid R_D) = \frac{R_D r_d}{R_{D+} r_d}$$

=  $\frac{(2 \times 10^3)(25 \times 10^3)}{(2 \times 10^3) + (25 \times 10^3)}$

$Z_0 = 1.85 \text{ k}\Omega$

•

$$r_d = \frac{1}{Y_{OS}} = 25 \text{ k}\Omega$$

•

$$Z_i = R_G = 1 M\Omega$$

•

$$A_V = -g_m(r_d \mid \mid R_D)$$

=  $-(1.88 \times 10^{-3})(1.85 \times 10^3)$

$A_V = -3.4$

•

$$A_V = -g_m R_D$$

=  $-(1.88 \times 10^{-3})(2 \times 10^3)$

$A_V = -3.76$

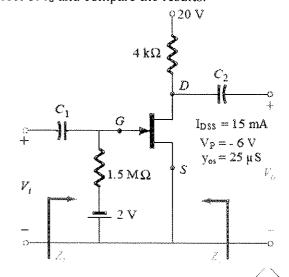

**Example 4.5** For the FET amplifier shown below:

a) Calculate Z<sub>i</sub>, Z<sub>o</sub> & A<sub>V</sub>

b) Calculate Z<sub>i</sub>, Z<sub>0</sub> & A<sub>V</sub>, by neglecting the effect of r<sub>d</sub> and compare the results.

Solution:

$$\begin{array}{ll} \mbox{Given:} & R_G = 1.5 \ \mbox{M}\Omega \\ I_{DSS} = 15 \ \mbox{mA} & R_D = 4 \ \mbox{k}\Omega \\ V_P = -6 \ \mbox{V} & V_{GG} = 2 \ \mbox{V} \\ y_{os} = 25 \ \mbox{\muS} & V_{DD} = 20 \ \mbox{V} \end{array}$$

a) For fixed bias circuit, We know that:

$$V_{GS} = -V_{GG}$$

$$V_{GS} = -2 V$$

$$g_{m0} = \frac{2^{1}DSS}{|V_{P}|}$$

$$= \frac{2 \times 15 \times 10^{-3}}{6}$$

$$g_{m0} = 5 \text{ mS}$$

$$g_{m} = g_{mo}(1 - \frac{V_{GS}}{V_{P}})$$

$$= (5 \times 10^{-3})(1 - \frac{-2}{-6})$$

$$g_{m} = 3.33 \text{ mS}$$

•

$$Z_0 = (r_d \mid\mid R_D) = \frac{R_D r_d}{R_{D+} r_d}$$

=  $\frac{(4 \times 10^3)(40 \times 10^3)}{(4 \times 10^3) + (40 \times 10^3)}$

$$Z_0 = 3.63 \text{ k}\Omega$$

•

$$r_d = \frac{1}{v_{os}} = (1/(25 \times 10^{-6})) = 40 \text{ k}\Omega$$

$$\sigma$$

$Z_i = R_G = 1.5 M\Omega$

$$A_{V} = -g_{m} (r_{d} | | R_{D})$$

$$= -(3.33 \times 10^{-3}) (3.63 \times 10^{3})$$

$$A_{V} = -12.08$$

Since  $r_d = 10 R_D$ , we can ignore the effect of  $r_d$ . Therefore we have, b)

•

$$Z_i = R_G = 1.5 M\Omega$$

•

$$Z_0 = R_D = 4 k\Omega$$

•

$$A_V = -g_m R_D$$

=  $-(3.33 \times 10^{-3})(4 \times 10^3)$

$A_V = -13.32$

The results are compared in the following table

| 1 | D         | 337:41                  | 337:414      |

|---|-----------|-------------------------|--------------|

|   | Parameter | With rd                 | Without rd   |

|   | $Z_{i}$   | $1.5~\mathrm{M}\Omega$  | 1.5 ΜΩ       |

|   | $Z_0$     | $3.63~\mathrm{k}\Omega$ | 4 k <b>Ω</b> |

|   | Αv        | -12.08                  | - 13.32      |

It is observed from the above table that both the results are approximately equal.

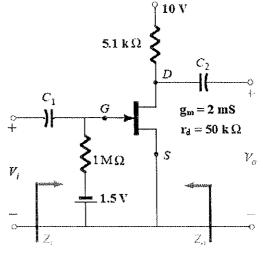

**Example 4.6** For the FET amplifier shown below: Calculate Zi, Zo & Av Solution:

$$\begin{array}{ll} \textbf{Given:} & R_G = 1 \ M\Omega \\ V_{GG} = 1.5 \ V & R_D = 5.1 \ k\Omega \\ V_{DD} = 10 \ V & g_m = 2 \ mS \\ r_d = 50 \ k\Omega & \end{array}$$

For fixed bias circuit, We know that:

$$V_{GS} = -V_{GG}$$

$$V_{GS} = -1.5 \text{ V}$$

•

$$Z_i = R_G = 1 M\Omega$$

•

$$Z_i = R_G = 1 \text{ M}\Omega$$

•  $Z_0 = (r_d \mid \mid R_D) = \frac{R_D r_d}{R_{D+} r_d}$

$$= \frac{(5.1 \times 10^3)(50 \times 10^3)}{(5.1 \times 10^3) + (50 \times 10^3)}$$

$$Z_0 = 4.628 \text{ k}\Omega$$

•

$$A_V = -g_m(r_d \mid \mid R_D)$$

=  $-(2 \times 10^{-3}) (4.628 \times 10^3)$

•  $A_V = -9.256$

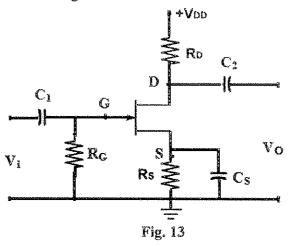

# 4.6 JFET Common Source Amplifier Using Self-bias Configuration (with bypassed Rs):

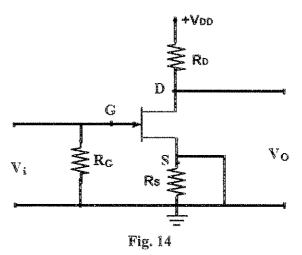

- The self-bias CS amplifier with input voltage Vi applied through coupling capacitor C<sub>1</sub> and connected to output through another coupling capacitor C<sub>2</sub> is shown in Fig. 13.

- The analysis of JFET CS amplifier for its small signal behavior can be made by following simple guidelines:

Guide line 1: Draw the actual circuit diagram.

Guide line 2: Replace Coupling capacitors and bypass capacitor with short circuit. (Because the capacitors are selected in such a way that they should offer very less reactance to the AC)

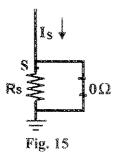

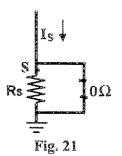

From the Fig. 15 it is observed that, after short circuiting coupling capacitor CS, the resistance  $R_S$  is in parallel with zero ohms. So their parallel combination is also zero. Therefore, resistance  $R_S$  in Fig. 14 can be replaced with 0  $\Omega$  as shown in Fig. 16.

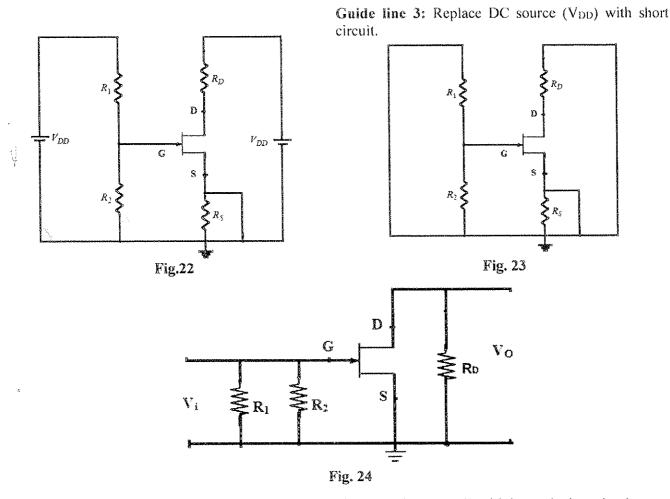

Guide line 3: Replace DC source (V<sub>DD</sub>) with short circuit.

Guide line 4: Replace FET terminals Gate (G), Drain (D) and Source (S) with its equivalent circuit.

Fig. 18

Note that the ac equivalent circuit of Fig.18 is exactly the same as that of JFET amplifier using fixed bias configuration, shown in Fig. 10. Hence the results derived in section 4.5 for  $Z_i$ ,  $Z_O$  &  $A_V$  can be readily applied to this circuit. Let us rewrite the results for reference.

Input Impedance (Z<sub>i</sub>):

$$Z_i = R_G$$

Output Impedance (Z<sub>0</sub>):

$$Z_0 = r_d \mid \mid R_D$$

$$Z_0 = \frac{R_D r_d}{R_D + r_d}$$

If rd ≥10RD,

Voltage gain (A<sub>V</sub>):

$$Av = -g_m (r_d \mid \mid R_D)$$

If  $r_d \ge 10 R_D$

$$A_V = -g_m R_D$$

C2

$l_{DO} = 2.5 \text{ mA}$

$I_{DSS} = 8 \text{ mA}$  $V_P = -5 \overline{V}$

$y_{os} = 20 \mu S$

Example 4.7 For the FET amplifier shown below: (a) Calculate Zi, Zo and Av. (b) Calculate Vo if Vi = 10 mV (p-p). (c) Calculate  $Z_i$ ,  $Z_o$ , and  $A_V$  by ignoring the effect of  $r_d$ .

$\mathbb{C}_1$

$Z_{i}$

Solution:

$$\begin{array}{ll} \textbf{Given:} & R_G = 5 \ \text{M}\Omega \\ I_{DQ} = 2.5 \ \text{mA} & R_D = 3.3 \ \text{k}\Omega \\ I_{DSS} = 8 \ \text{mA} & R_S = 1 \ \text{k}\Omega \\ V_P = -5 \ \text{V} & V_{DD} = 18 \ \text{V} \\ y_{os} = 20 \ \mu\text{S} & \end{array}$$

For Self bias circuit, We know that:

$$V_{GS} = -I_D R_S = -(2.5 \times 10^{-3} \times 1 \times 10^3)$$

$$V_{GS} = -2.5 \text{ V}$$

a)

$$g_{m0} = \frac{2I_{DSS}}{|V_P|}$$

$$= \frac{2 \times 8 \times 10^{-3}}{5}$$

$$g_{m0} = 3.2 \text{ mS}$$

•

$$g_m = g_{mo}(1 - \frac{V_{GS}}{V_P})$$

=  $(3.2 \times 10^{-3})(1 - \frac{-2.5}{-5})$

$g_m = 1.6 \text{ mS}$

•

$$\mathbf{r_d} = \frac{1}{Y_{OS}} = (1/20 \times 10^{-6}) = 50 \text{ k}\Omega$$

•

$$Z_i = R_G = 5 M\Omega$$

•

$$Z_0 = (r_d \mid \mid R_D) = \frac{R_D r_d}{R_{D+} r_d}$$

=  $\frac{(50 \times 10^3)(3.3 \times 10^3)}{(50 \times 10^3) + (3.3 \times 10^3)}$

•

$$Z_0 = 3.09 \text{ k}\Omega$$

$$A_{V} = -g_{m} (r_{d} | | R_{D})$$

$$= -(1.6 \times 10^{-3}) (3.09 \times 10^{3})$$

$$A_{V} = -4.944$$

$$A_{v} = \frac{V_{o}}{V_{i}}$$

Therefore,

c)

$$V_0 = A_V V_i$$

= - (4.944×10×10<sup>-3</sup>)

•

$$V_0 = -49.44 \text{ mV (p-p)}$$

When rd is neglected:

•

$$Z_i = R_G = 5 M\Omega$$

•

$$Z_0 = R_0 = 3.3 \text{ k}\Omega$$

•

$$A_V = -g_m R_D$$

=  $-(1.6 \times 10^{-3})(3.3 \times 10^3)$

$A_V = -5.28$

•

$$A_V = -g_m (r_d || R_D)$$

=  $-(1.6 \times 10^{-3}) (3.09 \times 10^3)$

$3.3 \text{ k}\Omega$

$\mathbb{G}$

≥5 MΩ

**Example 4.8** The self-bias configuration has an operating defined by  $V_{GSQ} = -2.6 \text{ V} \& I_{DQ} = 2.6 \text{ mA}$ , with  $I_{DSS} = 8 \text{ mA}$ ,  $V_P = -6 \text{ V}$ ,  $R_D = 3.3 \text{ k}\Omega$ ,  $R_G = 1 \text{ M}\Omega$ ,  $R_S = 1 \text{ k}\Omega$ ,  $V_{DD} = 20 \text{ V}$  and  $V_{$

$$\begin{array}{c} \text{Given:} & V_P = -6 \, V \\ I_{DQ} = 2.6 \, \text{mA} & y_{os} = 25 \, \mu \text{S} \\ I_{DSS} = 8 \, \text{mA} & R_S = 1 \, k\Omega \end{array} \\ \text{a)} & \bullet & g_{m0} = \frac{2I_{DSS}}{IV_{Pl}} \\ & \bullet & g_{m0} = \frac{2I_{DSS}}{56} \\ & g_{m0} = 2.67 \, \text{mS} \end{array} \\ & \bullet & g_m = g_{mo}(1 - \frac{V_{GS}}{V_P}) \\ & \bullet & g_m = g_{mo}(1 - \frac{V_{GS}}{V_P}) \\ & \bullet & r_d = \frac{1}{Y_{OS}} = (1/25 \times 10^{-6}) = 40 \, k\Omega \end{array} \\ & \bullet & \text{When rd is neglected:} \\ & \bullet & Z_0 = R_D = 3.3 \, k\Omega \end{array} \\ & \bullet & A_V = -g_m R_D \\ & \bullet & A_V = -g_m R_D \\ & \bullet & A_V = -g_m R_D \\ & \bullet & A_V = -4.6055 \end{array}$$

**Example 4.9** Determine the value of  $R_D$  for the circuit of figure below that will result in a gain of -10.

Solution:

Given:

$$R_G = 1 M\Omega$$

$I_{DSS} = 12 \text{ mA}$   $V_{GS} = -1V$

$V_P = -4 V$   $y_{os} = 20 \,\mu\text{S}$

$A_V = -10$

•  $g_{m0} = \frac{2I_{DSS}}{|V_P|} = \frac{2 \times 12 \times 10^{-3}}{4}$

$g_{m0} = 6 \,\text{mS}$

•  $g_m = g_{me}(1 - \frac{V_{GS}}{V_P})$

$= (6 \times 10^{-3})(1 - \frac{-1}{-4})$

$g_m = 4.5 \,\text{mS}$

•  $r_d = \frac{1}{Y_{OS}} = (1/20 \times 10^{-6}) = 50 \,\text{k}\Omega$

•  $A_V = -g_m \, (r_d \mid\mid R_D)$

$-10 = -(4.5 \times 10^{-3}) \, (r_d \mid\mid R_D)$

$-10 = -(4.5 \times 10^{-3}) \, (r_d \mid\mid R_D)$

$-10 = 2.23 \,\text{k}\Omega$

Therefore,

•  $R_D = 2.34 \,\text{k}\Omega$

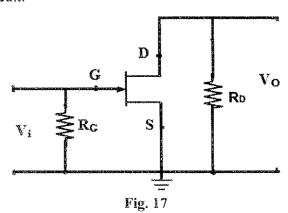

# 4.7 JFET Common Source Amplifier Using Voltage Divider bias Configuration (with bypassed $R_s$ ):

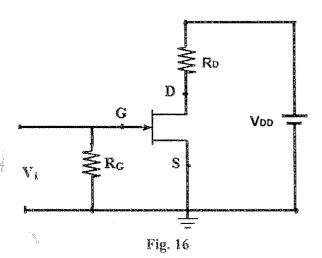

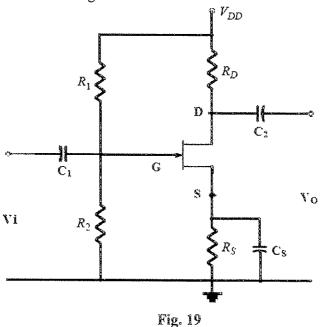

- The Voltage divider CS amplifier with input voltage Vi applied through coupling capacitor  $C_1$  and connected to output through another coupling capacitor  $C_2$  is shown in Fig. 19.

- The analysis of JFET CS amplifier for its small signal behavior can be made by following simple guidelines:

Guide line 1: Draw the actual circuit diagram.

Guide line 2: Replace Coupling capacitors and bypass capacitor with short circuit. (Because the capacitors are selected in such a way that they should offer very less reactance to the AC)

From the Fig. 21 it is observed that, after short circuiting coupling capacitor CS, the resistance  $R_S$  is in parallel with zero ohms. So their parallel combination is also zero. Therefore, resistance  $R_S$  in Fig. 20 can be replaced with  $0\ \Omega$ .

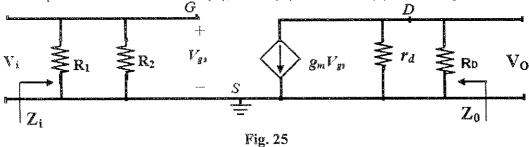

Guide line 4: Replace FET terminals Gate (G), Drain (D) and Source (S) with its equivalent circuit.

Note that the ac equivalent circuit of Fig. 25 is exactly the same as that of JFET amplifier using fixed bias configuration, shown in Fig. 10. Hence the results derived in section 4.5 for  $Z_i$ ,  $Z_O$  &  $A_V$  can be readily applied to this circuit. The only exception is that,  $R_G$  should be replaced by  $R_1 \mid\mid R_2$ . Let us rewrite the results for reference.

- Input Impedance ( $Z_i$ ):  $Z_i = (R_1 | | R_2)$

- Output Impedance ( $Z_0$ ):  $Z_0 = (r_d \mid \mid R_D)$

If  $r_d \ge 10R_D$ ,  $Z_0 \approx R_D$

• Voltage gain (A<sub>V</sub>):  $A_V = -g_m (r_d || R_D)$

If  $r_d \ge 10 R_D$   $A_V = -g_m R_D$

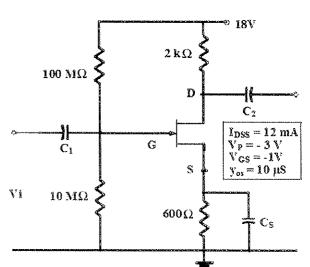

**Example 4.10** For the JFET amplifier shown below: (a) Calculate  $Z_i$ ,  $Z_O$  and  $A_V$ . (b) Find  $V_O$  if  $V_i = 25 \text{ mV}$ .

Solution:

Given:

$$I_{DSS} = 12 \text{ mA}$$

$$V_P = -3 \text{ V}$$

$$V_{GS} = -1 \text{ V}$$

$$V_{DD} = 18 \text{ V}$$

$$R_1 = 100 \text{ M}\Omega$$

$$R_2 = 10 \text{ M}\Omega$$

$$R_D = 2 \text{ k}\Omega$$

$$R_S = 600 \Omega$$

$$y_{os} = 10 \text{ \mu}S$$

$$\mathbf{g}_{m0} = \frac{2I_{DSS}}{|V_{P}|} = \frac{2 \times 12 \times 10^{-3}}{3}$$

$$\mathbf{g}_{m0} = \mathbf{8 \ mS}$$

$$g_{m} = g_{mo}(1 - \frac{V_{GS}}{V_{P}})$$

$$= (8 \times 10^{-3})(1 - \frac{-1}{-3})$$

$$g_{m} = 5.33 \text{ mS}$$

•

$$r_d = \frac{1}{Y_{OS}} = (1/10 \times 10^{-6}) = 100 \text{ k}\Omega$$

•

$$Z_i = (R_1 || R_2)$$

$Z_i = (100 \text{ M}\Omega || 10 \text{ M}\Omega)$

$Z_i = 9.09 \text{ M}\Omega$

•

$$Z_O = (r_d | | R_D)$$

$Z_O = (100 kΩ | | 2 kΩ)$

$Z_O = 1.96 kΩ$

•

$$A_V = -g_m (r_d \mid \mid R_D)$$

=  $-(5.33 \times 10^{-3}) (1.95 \times 10^3)$

•

$$A_V = -10.44$$

We know that,

•

$$A_v = \frac{V_0}{V_i}$$

Therefore,

$$V_0 = A_V V_i$$

= - (10.44×25×10<sup>-3</sup>)

•

$$V_0 = -0.261 \text{ V}$$

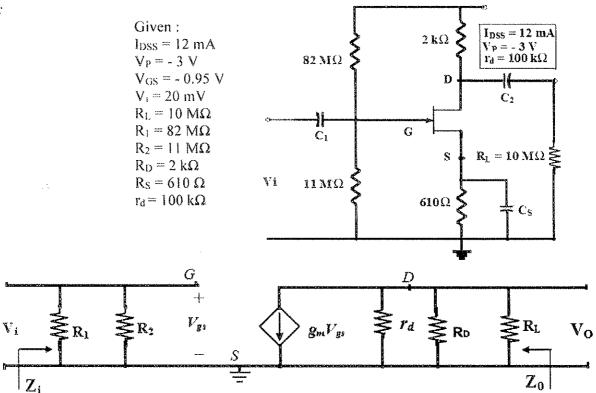

**Example 4.11** Determine  $Z_i$ ,  $Z_O$  and  $V_O$  for the network shown below: if  $V_i = 20$  mV and  $V_{GSQ} = -0.95$  V.

Solution:

$$\label{eq:gm0} \begin{array}{ll} \bullet & g_{m0} = \frac{2I_{DSS}}{|V_P|} = \frac{2\times12\times10^{-3}}{3} \\ & g_{m0} = 8~mS \end{array}$$

•

$$g_m = g_{mo}(1 - \frac{V_{GS}}{V_P})$$

=  $(8 \times 10^{-3})(1 - \frac{-0.95}{-3})$

$g_m = 5.47 \text{ mS}$

•

$$Z_i = (R_1 || R_2)$$

$Z_i = (11 M\Omega || 82 M\Omega)$

$Z_i = 9.7 M\Omega$

•

$$Z_O = (r_d || R_D || R_L)$$

$Z_O = (100 kΩ || 2 kΩ || 10 MΩ)$

$Z_O = 1.97 kΩ$

$$A_V = -g_m (r_d \mid \mid R_D \mid \mid R_L)$$

$$= -(5.47 \times 10^{-3}) (1.97 \times 10^3)$$

$$\bullet$$

Av = -10.77

We know that,

•

$$A_v = \frac{V_O}{V_i}$$

Therefore,

•

$$V_o = A_V V_i$$

= -(10.77×20×10<sup>-3</sup>)

$$v_0 = -0.21538 \text{ V}$$

$$V_0 = -215.38 \text{ mV}$$